- PRODUCTS

- RECORDERS

- SUPPORT

| Home > Pipeline Newsletters > The Pentek Pipeline Vol. 27 No. 2 |

Sign-Up for SOSA (Sensor Open Systems Architecture) Updates! Sign-Up for Quartz Zynq UltraScale+ RFSoC Updates! Sign-Up for Jade Kintex UltraScale Updates!  Sign-Up for Cobalt Virtex-6 Updates!  Sign-Up for Onyx Virtex-7 Updates!  Sign-Up for Talon System Updates!  Sign-Up for Flexor FMC Updates!  Sign-Up for the Pipeline Newsletter! Free Technical Resources:

Putting VPX and OpenVPX to Work Handbook  High-Speed, Real-Time Recording Systems Handbook  High-Speed Switched Serial Fabrics Improve System Design  Software Defined Radio Handbook  Putting FPGAs to Work for Software Radio Handbook  Critical Techniques for High Speed A/D Converters in Real-Time Systems Handbook Pentek Literature: |

Strategies for Deploying Xilinx's Zync UltraScale+ RFSoCby Bob SgandurraOn February 21st, 2017, Xilinx® announced the introduction of a new technology called RFSoC with the rather dramatic headline "Xilinx Unveils Disruptive Integration and Architectural Breakthrough for 5G Wireless with RF-Class Analog Technology." The proposition was simple: add RF-class analog to digital and digital to analog data converters to Xilinx's already powerful MPSoC, ARM processor enhanced family of high performance FPGAs. And while the concept was simple, the implications were profound, changing the way engineers could design and package small, high channel count systems. And this technology not only offers new possibilities for 5G applications, but has significant impact in military and scientific systems, justifying the claim in Xilinx's announcement. To get better appreciation of the capabilities of RFSoC and understand how to best use the advantages of this technology, it's worth taking a quick look at current trends in data converters and signal processing. Product Focus

8 Channel A/D and D/A Zynq UltraScale+ RFSoC Processor

Product Focus

2-Channel 200 MHz A/D with 766 DDCs, Kintex UltraScale FPGA

Product Focus

Kintex UltraScale FPGA Coprocessor

With Pentek's New Jade Architecture Came a New Documentation Architecture What has changed?

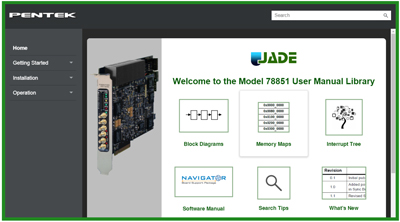

Why the change? The AXI4* implementation in the Jade architecture distributes control registers throughout the block diagrams, which is different from a centralized control register memory map. Because of this, the address information must be navigated in a different way than in the past and using an HTML, linkable format puts the register information right at your fingertips. *AXI4 is the fourth generation of an interface specification from ARM® commonly used in the semiconductor industry. Xilinx has adopted this standard to create AXI4-compliant plug-and-play IP. Navigator® FDK follows the AXI4 standard. For Pentek's Jade products, the FDK includes the complete IP that is factory-installed in the board. This includes all interface, processing, data formatting, DMA functions, etc. IP designers can modify or replace functions as needed to match application requirements, and will find immediate compatibility with Xilinx IP and third-party IP that uses AXI4. Designers who create their own custom IP using the AXI4 standard will find integration with the Pentek-supplied IP straightforward. How is it organized? The picture below shows the user manual library for Jade Model 78851. To the left, the table of contents panel lists the HTML manuals: Getting Started, Installation, and Operation. The center of the screen provides easy access to block diagrams, memory maps, the interrupt tree, and the Navigator® BSP software manual.  How do I get it? Each Jade product is shipped with a DVD containing its user manual library. If you sign up to receive product update notifications via YourPentek, when the library is updated, you'll get an email notification. Clicking on the link in the email will download a short document that describes the user manual library and tells you what has been updated in it (to see an example, click here). The document also contains instructions for how to download a zip file that contains the updated library. We are excited about this new format for our documentation because we believe it will better serve our customers. |

| CONNECT ON SOCIAL: |

|

|

|

|