#### **Features**

- Complete GSM channelizer with analog IF interface

- Four 180 MHz 16-bit A/Ds

- Two banks of 375 DDCs for upper GSM band

- Two banks of 175 DDCs for lower GSM band

- Sample clock synchronization to an external system reference

- LVPECL clock/sync bus for multiboard synchronization

- PCI Express Gen. 2 x8

# **General Information**

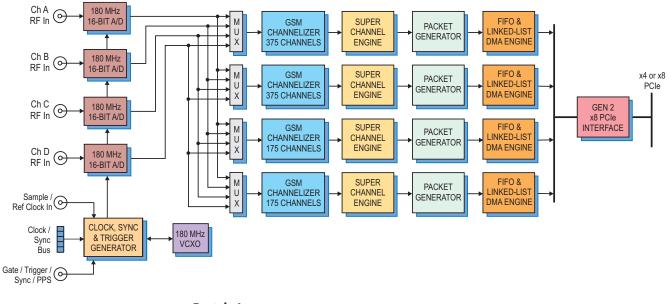

Model 78663 is a member of the Cobalt<sup>®</sup> family of high-performance PCIe boards based on the Xilinx Virtex-6 FPGA. This fourchannel, high-speed A/D converter with 1100 GSM DDCs (digital downconverters) accepts IF signals from an RF tuner. It is ideal for capturing all transmit and receive signals in both upper and lower GSM bands.

It includes four A/Ds and four banks of DDCs. Channelizer data and control signals flow across the PCI Express Gen. 2 native interface, providing peak rates of up to 4 GB/sec.

### The Cobalt Architecture

The Pentek Cobalt architecture connects all of the board's data converters, digital interfaces, clocks and timing signals to the FPGA. Here, four factory-installed GSM channelizer IP cores are supported with additional FPGA functions including packet formation, four DMA controllers, PCIe interface, gating, and triggering.

The 78663 is a complete, full-featured subsystem, ready to use with no additional FPGA development required.

### A/D Converter Stage

The front end accepts four analog IF inputs on front panel SSMC connectors with transformer coupling into four Texas Instruments ADS5485 200 MHz, 16-bit A/D converters clocked at 180 MHz.

The digital outputs are delivered into the FPGA for GSM channelizer signal processing.

# **Clocking and Synchronization**

An internal timing bus provides all timing and synchronization required by the A/D converters. It includes a clock, two sync and two gate or trigger signals. An on-board clock generator accepts an external 180 MHz sample clock from the front panel SSMC connector. This clock can be used directly by the A/D or divided by a built-in clock synthesizer circuit. In an alternate mode, the sample clock can be sourced from an on-board 180 MHz voltagecontrolled crystal oscillator. In this mode, the front panel SSMC connector can be used to provide a reference clock, typically 10 MHz, for synchronizing the internal oscillator.

A front panel 26-pin LVPECL Clock/Sync connector allows multiple boards to be synchronized. In the slave mode, it accepts LVPECL inputs that drive the clock, sync and gate signals. In the master mode, the LVPECL bus can drive the timing signals for synchronizing multiple boards.

Multiple 78663's can be driven from the LVPECL bus master, supporting synchronous sampling and sync functions across all connected boards.

### **GSM Channelizer Cores**

The 78663 contains four powerful GSM channelizer cores, two with 375 DDCs and two with 175 DDCs. Flexible input routing allows the independent, non-blocking assignment of any A/D converter to serve as the input source for any of the four GSM channelizers.

➤ The 375-channel cores are designed for the upper GSM bands which contain two 75 MHz bands, one for uplink and one for downlink. The 175-channel cores are designed for the lower GSM band and handle two 35 MHz bands, one for uplink and one for downlink.

Before connection to the 78663, these GSM RF bands must first be separately downconverted to an IF frequency centered at 45 MHz, 135 MHz or 225 MHz using an external analog RF tuner.

These IF signals are then digitized by the 78663 A/Ds at 180 MS/sec in the first, second, or third Nyquist zones, respectively. In order to prevent aliasing, careful filtering must ensure that no signals appear in adjacent Nyquist zones.

Each of the channelizers is designed to accept real digital samples of the IF signal from the A/D converter. The first stage of the GSM channelizer is a complex mixer that shifts the center frequency of the IF signal (45, 135 or 225 MHz) to 0 Hz, thereby producing complex I+Q samples.

The DDCs split the IF input into either 175 or 375 parallel DDC baseband channels, equally spaced at 200 kHz. The DDC output sample rate is resampled to precisely 180 MHz\*13/2160, or approximately 1.08333 MHz. This is four times the GSM symbol rate of 270.666 kSymbols/sec. The output passband of each DDC channel is nominally 160 kHz, with filter characteristics fully defined in the channel response chart in the specifications.

### **Channelizer Output Formatting**

All 1100 DDCs generate parallel, complex output sample streams. At a sample rate of 1.08333 MS/sec, this represents an aggregate output rate of 9.533 GB/sec, greatly exceeding the 4 GB/sec peak rate of PCIe Gen 2 x8 interface.

To mitigate this situation, every four DDC channels are frequency-mutliplexed into a single "superchannel". This is allowed because of the 4x oversampling, and results in a reduction of the aggregate PCIe traffic by a factor of 4 to 2.383 GB/sec, which is now well within the capability of the PCIe Gen 2 x8 interface.

During superchannel formation, the 24-bit I + 24-bit Q output samples from four DDCs are summed to superchannel samples with 26-bit I + 26-bit Q.

As a result, the two 375-channel banks each deliver 94 superchannels, while the two 175-channel banks each deliver 44 superchannels. The last superchannel in each bank contains only three DDC channels.

A superchannel enable mask word containing one enable bit for each superchannel allows independent selection of which superchannel samples are delivered across the PCIe. There are four superchannel mask words, one for each bank.

#### **Superchannel Packets and Headers**

Superchannel packets are formed by appending enabled superchannel samples sequentially from each bank. Once complete, a unique superchannel packet header is inserted at the beginning of each packet for identification.

The header contains a time stamp, a sequential packet count, the number of enabled superchannels, the DMA channel identifier, and other information. By inspecting the header, the remaining superchannel data "payload" samples can be identified and recovered by the host.

### **PCI Express Interface**

The Model 78663 includes an industrystandard interface fully compliant with PCI Express Gen. 2 bus specifications. Supporting PCIe links up to x8, the interface includes four DMA controllers for efficient packet transfers from each of the four DDC banks to system memory.

The PCIe interface is also used as the programming interface for all status and control between the 78663 and host. >

www.pentek.com

### **Model 8266**

The Model 8266 is a fullyintegrated PC development system for Pentek Cobalt, Onyx and Flexor PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

► Specifications Front Panel Analog Signal Inputs Input Type: Transformer-coupled, front panel female SSMC connectors Transformer Type: Coil Craft WBC4-6TLB Full Scale Input: +8 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz A/D Converters Type: Texas Instruments ADS5485 Sampling Rate: 10 MHz to 200 MHz Resolution: 16 bits Sample Clock Sources: On-board clock synthesizer Clock Synthesizer Clock Source: Selectable from on-board 180 MHz VCXO, front panel external clock or LVPECL timing bus Synchronization: VCXO can be locked to an external 10 MHz system reference External Clock Type: Front panel female SSMC connector, sine wave, 0 to +10 dBm, 50 ohms, AC-coupled, accepts 180 MHz sample clock or 10 MHz system reference Timing Bus: 26-pin front panel connector; LVPECL bus includes, clock/sync/gate/ PPS inputs and outputs; TTL signal for gate/trigger and sync/PPS inputs **External Trigger Input** Type: Front panel female SSMC connector, LVTTL Function: Programmable functions include: trigger, gate, sync and PPS **GSM** Channel Banks DDCs per bank: two banks of 175 DDCs and two banks of 375 DDCs Overall bandwidth per bank: 35 MHz & 75 MHz for 175- & 375-channel banks IF (Center) Freq: 45, 135 or 225 MHz

**DDC Channels** Channel Spacing: 200 kHz, fixed **DDC Center Freqs:** IF Freq ± k \* 200 kHz, where k = 0 to 87, or 0 to 187 **DDC Channel Filter Characteristics** < 0.1 dB passband flatness across ±80 kHz from center (160 kHz BW) > 18 dB attenuation at ±100 kHz > 78 dB attenuation at ±170 kHz > 83 dB attenuation at ±600 kHz > 93 dB attenuation at ±800 KHz > 96 dB attenuation at  $> \pm 3$  MHz DDC Output Rate fs: Resampled to 180 MHz\*13/2160 = 1.0833333 MS/sec DDC Data Output Format: 24 bits I + 24 bits Q Superchannels Content: Four consecutive DDC channels are frequency-offset from each other and then summed together Frequency Offsets for each DDC: First: -f<sub>s</sub>/4 (-270.8333 kHz) Second: 0 Hz Third:  $+f_s/4$  (+270.8333 kHz) Fourth:  $+f_s/2$  (+541.666 kHz) Superchannel Sample Rate: *f*<sub>s</sub> Superchannel Output Format: 26 bits I + 26 bits Q Number of Superchannels per Bank: 175-Channel banks: 44; 375-Channel banks: 94 Field Programmable Gate Array: Xilinx Virtex-6 XC6VSX315T **PCI Express Interface** PCI Express Bus: Gen. 2 x8 Environmental **Operating Temp:** 0° to 50° C Storage Temp: –20° to 90° C Relative Humidity: 0 to 95%, non-cond. Size: Half length PCIe card, 4.38 x 7.13 in.

### **Ordering Information**

| Model  | Description           |

|--------|-----------------------|

| 78663  | 1100-Channel GSM      |

|        | Channelizer with Quad |

|        | A/D- PCIe             |

| 78663G | RoHS version, contact |

|        | factory               |

| Model | Description           |

|-------|-----------------------|

| 8266  | PC Development System |

|       |                       |

See 8266 Datasheet for Options