## Models 72611, 73611 and 74611

Model 74611 Model 73611

#### **Features**

- Four or eight channels of Serial FPDP interface

- Fully compliant with VITA 17.1 specification

- Fiber optic or copper serial interfaces

- One or two Virtex-6 FPGAs

- Up to 2 or 4 GB of DDR3 SDRAM

- LVDS connections to the Virtex-6 FPGA for custom I/O

## **General Information**

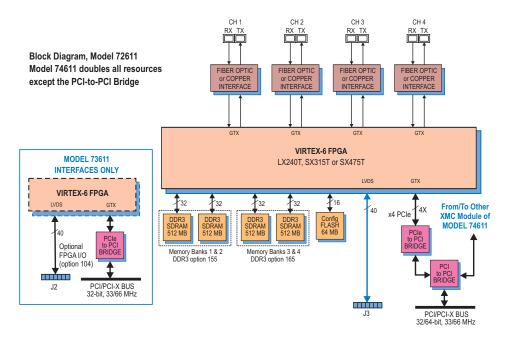

Models 72611, 73611 and 74611 are members of the Cobalt<sup>®</sup> family of highperformance CompactPCI boards based on the Xilinx Virtex-6 FPGA. They consist of one or two Model 71611 XMC modules mounted on a cPCI carrier board.

Model 72611 is a 6U cPCI board while the Model 73611 is a 3U cPCI board; both are equipped with one Model 71611 XMC. Model 74611 is a 6U cPCI board with two XMC modules rather than one.

These models are fully compatible with the VITA 17.1 Serial FPDP specification. Their built-in data transfer features make them complete turnkey solutions. For users who require application-specific functions, they serve as flexible platforms for developing and deploying custom FPGA processing IP.

## The Cobalt Architecture

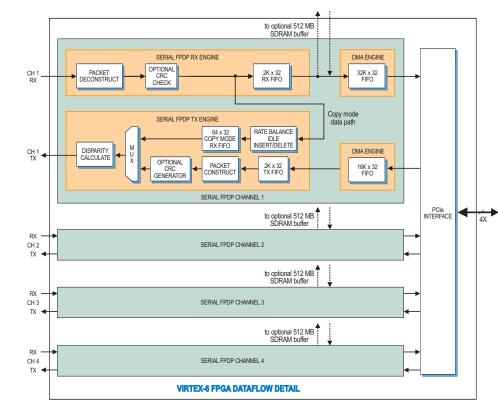

The Pentek Cobalt Architecture features one or two Virtex-6 FPGAs. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data transfer and memory control. The Cobalt Architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

IP modules for DDR3 SDRAM memories, controllers for data routing and flow control, CRC support, advanced DMA engines, and a cPCI interface complete the factory-installed functions and enable these models to operate as a complete turnkey solutions without the need to develop any FPGA IP.

## **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow® FPGA Design Kits include all of the factoryinstalled modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow kit to completely replace the Pentek IP with their own.

## **Xilinx Virtex-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX240T, SX315T, or SX475T. The SXT parts feature up to 2016 DSP48E slices and are ideal for modulation/demodulation, encoding/ decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, the lowercost LXT FPGA can be installed.

Option -104 provides 20 LVDS pairs between the FPGA and the J2 connector, Model 73611; J3 connector, Model 72611; J3 and J5 connectors, Model 74611. >

## ► Serial FPDP Interface

These models are fully compatible with the VITA 17.1 Serial FPDP specification. With the capability to support 1.0625, 2.125, 2.5, 3.125, and 4.25 Gbaud link rates and the option for multi-mode and single-mode optical interfaces, the boards can work in virtually any system. Programmable modes include: flow control in both receive and transmit directions, CRC support, and copy/loop modes.

#### **Memory Resources**

The architecture supports up to four or eight independent memory banks of DDR3 SDRAM. Each memory is 512 MB deep and an integral part of the board's DMA capabilities, providing FIFO memory space for creating DMA packets.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes.

#### **PCI-X Interface**

These models include an industry-standard interface fully compliant with PCI-X bus specifications. The interface includes multiple DMA controllers for efficient transfers to and from the board. Data widths of 32 or 64 bits (32 bits only, Model 73611) and data rates of 33 and 66 MHz are supported.

### **Specifications**

- Front Panel Serial FPDP Inputs/Outputs Number of Connectors: 4 or 8 Fiber Optic Connector Type: LC

- Laser: 850 nm (standard, other options available)

Copper Connector Type: Micro Twinax Fiber Optic or Copper Link Rates: 1.0625, 2.125, 2.5, 3.125 or 4.25 Gbaud (copper rate depends on cable langth) Fiber Optic or Copper Data Transfer Rates: 105, 210, 247, 309 or 420 MB/sec (depending on link rate) per serial FPDP port

Field Programmable Gate Array: Xilinx Virtex-6 XC6VLX240T, XC6VSX315T, or XC6VSX475T

#### Custom I/O

**Option -104:** provides 20 LVDS pairs between the FPGA and the J2 connector, Model 73611; J3 connector, Model 72611; J3 and J5 connectors, Model 74611

#### Memory

Option 155 or 165: Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR PCI-X Interface

PCI-X Bus: 32- or 64-bit at 33 or 66 MHz Model 73611: 32-bit at 33 or 66 MHz Environmental

Operating Temp: 0° to 50° C Storage Temp: −20° to 90° C Relative Humidity: 0 to 95%, non-cond. Size: Standard 6U or 3U cPCI board ➤

## **Ordering Information**

| Model    | Description                                                                                                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| 72611    | Quad Serial FPDP<br>Interface with Virtex-6<br>FPGA - 6U cPCI                                                                       |

| 73611    | Quad Serial FPDP<br>Interface with Virtex-6<br>FPGA - 3U cPCI                                                                       |

| 74611    | Octal Serial FPDP<br>Interface with Virtex-6<br>FPGA - 6U cPCI                                                                      |

| Options: |                                                                                                                                     |

| -062     | XC6VLX240T FPGA                                                                                                                     |

| -064     | XC6VSX315T FPGA                                                                                                                     |

| -065     | XC6VSX475T FPGA                                                                                                                     |

| -104     | LVDS I/O between the<br>FPGA and J2 connector<br>Model 73611; J3<br>connector, Model 72611;<br>J3 and J5 connectors,<br>Model 74611 |

| -155     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2)                                                                            |

| -165     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4)                                                                            |

| -280     | Copper serial interfaces                                                                                                            |

| 004      |                                                                                                                                     |

-281 Multi-mode optical serial interfaces

Pentek, Inc. One Park Way Upper Saddle River New Jersey 07458 Tel: 201/818/5900 Fax: 201/818/5904 Email: info@pentek.com Models 72611, 73611 and 74611

# ► Serial FPDP VITA 17.1 Compliance The 71611 fully complies with the VITA 17.1 specification as follows: What Link Rate does the interface support? ■ 1.0625 Gbaud ■ 2.125 Gbaud ■ 2.5 Gbaud ■ 3.125 Gbaud ■ 4.25 Gbaud What Serial FPDP function does the interface support? \_\_\_\_ Transmitter only \_\_\_\_ Receiver only \_\_\_\_ Transmitter & Receiver Does the Receiver support Flow Control (setting the STOP signal)? \_\_\_\_Always active \_\_\_\_Not supported \_\_\_\_Optional (selectable) Does the Transmitter support Flow Control (stopping data transmission on receipt of a STOP signal)? \_\_\_\_Always active \_\_\_\_Not supported \_\_\_\_Optional (selectable) If the Transmitter supports Flow Control, after transmitting a STOP signal, how many 32-bit words can be received before a **Receive FIFO overflow occurs?** Programmable Does the interface support CRC? \_\_\_\_Always active \_\_\_\_Not supported \_\_\_\_ Optional (selectable) Does the Transmitter support Copy Master Mode (insertion of additional IDLE ordered sets)? \_\_\_\_Always active \_\_\_\_Not supported \_\_\_\_Optional (selectable) Does the Receiver support Copy Mode (retransmission of data)? Yes No If Copy Mode is supported, what method is used for implementation (see VITA 17.1 Observation 6.1.4.4)? \_\_ Method 1 \_\_ Method 2 Does the Receiver support Copy/Loop Mode (retransmission of data and setting Flow Control)? ∎ Yes \_\_No What type of media is supported? ■ Short Wave Laser ■ Long Wave Laser ■ Copper What type of media connectors are supported? ■ LC \_\_ SC \_\_ ST \_ Micro Twinax Which fiber transmit data frames are supported in addition to Normal Data Fiber Frames (see VITA 17.1 Permission 7.3.3.1)? Sync without Data Fiber Frames Sync with Data Fiber Frames Does the Serial FPDP Transmitter stop in response to the Serial FPDP Receiver sending NRDY True (see VITA 17.1 Observation 7.3.2.2)?

\_\_\_\_Always \_\_\_ Never \_\_\_\_ Optional (selectable)

Are status bits kept up to date when there is no data to transmit by sending empty Serial FPDP Normal Data Fiber (see VITA 17.1 Rule 7.3.3.8, Recommendation 7.3.3.2 and Suggestion 7.3.3.1)?

Yes, empty frames transmitted \_\_\_\_\_No, status is not updated when no data is transmitted