Model 52624 COTS (left) and rugged version

#### **Features**

- Modifies 34 IF signals between input and output

- Up to 80 MHz IF bandwidth

- Two 200 MHz 16-bit A/Ds

- Two 800 MHz 16-bit D/As

- 34 DDCs and 34 DUCs (digital downconverters and digital upconverters)

- Signal drop/add/replace

- Frequency shifting and hopping

- Amplitude boost and attenutation

- PCI Express Gen. 1: x4 or x8,

### **General Information**

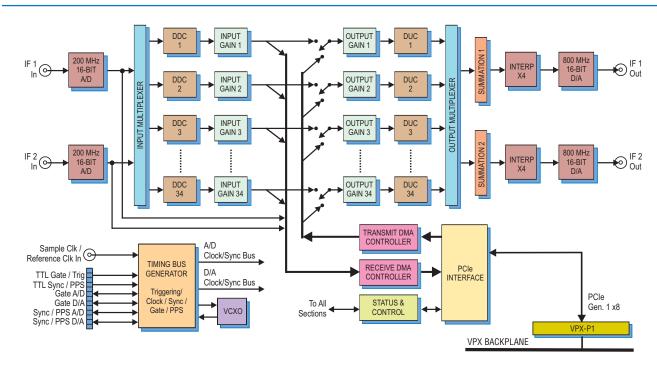

Model 52624 is a member of the Cobalt<sup>®</sup> family of high-performance 3U OpenVPX boards based on the Xilinx Virtex-6 FPGA. As an IF relay, it accepts two IF analog input channels, modifies up to 34 signals, and then delivers them to two analog IF outputs. Any signal within each IF band can be independently enabled or disabled, and changed in both frequency and amplitude as it passes through the module.

The 52624 supports many useful functions for both commercial and military communications systems including signal drop/add/replace, frequency shifting and hopping, amplitude equalization, and bandwidth consolidation. Applications include countermeasures, active tracking and monitoring, channel security, interception, adaptive spectral management, jamming, and encryption.

The Pentek Cobalt product family features the Virtex-6 FPGA. All of the board's data converters, interfaces and control lines are connected to the FPGA, which performs the data-routing and DSP functions for the adaptive relay.

A PCIe Gen 1 system interface supports control, status and data transfers.

# **Adaptive Relay Input Overview**

The Model 52624 digitizes two analog IF inputs using two 200 MHz 16-bit A/D converters. The bandwidth of each IF signal can be up to 80 MHz, and may contain multiple signals, each centered at a different frequency. An array of 34 DDCs (digital downconverters) can be independently

programmed to translate any signal to baseband and then bandlimit the signal as required. DDC tuning frequency is programmable from 0 Hz to the A/D sample rate. Output bandwidth is programmable from around 20 kHz to 312 kHz for a sample rate of 200 MHz. Each DDC can independently source IF data from either of the two A/Ds.

Baseband I+Q DDC outputs are scaled in a programmable gain/attenuation block before being delivered across the PCIe system interface to target memory, typically associated with a system processor. Here, the signals can be analyzed, classified, demodulated, decrypted or decoded, depending on the application.

Samples from each A/D converter can also be delivered across PCIe to system memory so that the processor can access wideband IF data. By performing an FFT, the processor can identify signals and then tune the DDCs accordingly.

# **Adaptive Relay Output Overview**

The Model 52624 output stage consists of 34 DUCs (digital upconverters) and two 800 MHz 16-bit D/A converters. Each DUC accepts baseband I+Q signals from either the local DDCs or from system memory.

DUC inputs are scaled in programmable gain/attenuation blocks similar to those in the input stage. Each DUC is independently programmable for data source selection (DDC or memory), upconvert tuning frequency and bandwidth (interpolation).

The translated DUC outputs are directed to either of two summation blocks, each >

# Dual-Channel, 34-Signal Adaptive IF Relay - 3U OpenVPX

➤ associated with one of the two D/A converters using a final interpolation factor of x4. After conversion, the IF analog outputs of each D/A can contain signals from any combination of the 34 DUCs.

### Xilinx Virtex-6 FPGA

The SX315T Virtex-6 FPGA with 1344 DSP48E engines is well suited for the demanding signal processing tasks required by the Model 52624 adaptive relay. Because of the complexity and proprietary nature of these functions, the FPGA cannot be extended or modified by the user.

### **A/D Converters**

The front-end accepts two analog HF or IF inputs on front panel SSMC connectors with transformer-coupling into two Texas Instruments ADS5485 200 MHz, 16-bit A/D converters.

The digital outputs are delivered into the Virtex-6 FPGA for the data capture and all of the remaining adaptive relay signal processing operations.

# **Digital Downconverters**

Each of the FPGA-based DDCs has an independent mixer and local oscillator with a 32-bit tuning frequency setting that ranges from DC to  $f_{\rm s}$ , where  $f_{\rm s}$  is the A/D sampling frequency, nominally 200 MHz. An IF input signal can be downconverted to a complex (I+Q) signal centered at 0 Hz by setting the DDC tuning frequency to its center frequency.

The DDC output bandwidth is determined by its decimation setting, which is programmable from 512 to 8192 in steps of 8. Each DDC can have a different decimation, thereby supporting up to 34 different signal bandwidths.

The fixed 80% decimating output filters deliver an output bandwidth equal to  $0.8*f_{\rm s}/{\rm N}$ , where N is the decimation setting and  $f_{\rm s}$  is the A/D sample rate. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB.

Each DDC delivers a complex output stream consisting of 16-bit I + 16-bit Q samples at a rate of  $f_s/N$ .

### **Input Gain Blocks**

Each DDC complex output is delivered through a complex gain stage where the baseband signal can be amplified or attenuated. Each input gain block, which is a complex digital multiplier, accepts a unique 16-bit binary gain coefficient in Q8.8 format (8 bits integer + 8 bits fractional). This results in

gain values ranging from approximately +48 dB to -48 dB.

### **Receive DMA Controller**

Two output DMA engines deliver data across the PCIe interface into user-specified memory locations in PCIe target memory. DMA engine #1 can deliver either raw samples from A/D Ch 1 or channel-interleaved 24-bit I and Q baseband samples from the 34 DDCs. Data samples from each DDC can be independently enabled/disabled for output. DMA engine #2 can deliver raw samples from A/D Ch 2.

When a target memory buffer is filled, the 52624 issues an interrupt to the system processor and then begins filling an alternate buffer. In this way, the processor is always informed when and where data is available for retrieval. Packet headers identify the DDC and show the number of subsequent data samples.

### **Transmit DMA Controller**

Each of the FPGA-based 34 DUCs interpolates complex (I+Q) baseband signals and translates them to the desired IF output center frequency.

The data source for each DUC can be independently selected from its corresponding DDC output, or from PCIe target memory buffers fetched by the transmit DMA controller, where header information steers the memory data to the appropriate DUC channel.

Like the receive DMA controllers, once a data buffer is emptied, the 52624 signals the processor with an interrupt and moves to the next assigned buffer to continue fetching data.

### **Output Gain Blocks**

The complex baseband input for each DUC complex output is delivered through a complex gain stage where the baseband signal can be amplified or attenuated.

Each of the output gain blocks accepts a unique 16-bit binary gain coefficient in Q8.8 format (8 bits integer + 8 bits fractional). This results in gain values ranging from approximately +48 dB to -48 dB.

### **Digital Upconverters**

The interpolation filter increases the baseband input sample rate by an interpolation factor typically equal to the decimation factor of the corresponding DDC. This interpolation factor is programmable from 512 to 8192 in steps of 8. Using this strategy, the interpolation sample rate equals the A/D sample rate, nominally 200 MHz.

# Dual-Channel, 34-Signal Adaptive IF Relay - 3U OpenVPX

▶ A complex digital mixer upconverts the interpolated baseband signal to the desired IF output center frequency. This frequency is determined by a local oscillator programmable with a 32-bit integer from DC to  $f_{sr}$  where  $f_{s}$  is the interpolator output frequency, nominally 200 MHz.

Each of the DUCs can have an independent interpolation factor and tuning frequency. However, all DUC outputs sharing a common summation block must have the same sample rate.

# **Summation Blocks**

Two summation blocks accept any combination of the upconverted DUC signals by setting an enable bit for each DUC's contribution. Each DUC output can be enabled for none, one or both of the summation blocks.

The summation blocks deliver only real output samples to the subsequent D/A converter stage.

### **D/A Converters**

A TI DAC5688 dual-channel D/A accepts two summed upconverted data streams, one from each summation block, and operates in its non-translating dual, real baseband mode. Its built-in interpolation filter is typically set to x4 mode, boosting the summation output sample rate from a nominal 200 MHz to 800 MHz. This simplifies the output low pass reconstruction filtering requirements.

Two transformer-coupled analog IF outputs are delivered through a pair of front panel SSMC connectors.

## **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives an external sample clock from the front panel SSMC connector. This clock can be used directly for either the A/D or D/A sections or can be divided by a built-in clock synthesizer circuit to provide different A/D and D/A clocks.

In an alternate mode, the sample clock can be sourced from an on-board programmable VCXO (voltage-controlled crystal oscillator). In this mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the internal oscillator.

A front panel 26-pin LVPECL Clock/Sync connector allows multiple boards to be synchronized. In the slave mode, it accepts LVPECL inputs that drive the clock, sync and gate signals. In the master mode, the LVPECL bus can drive the timing signals for synchronizing multiple boards.

Multiple 52624's can be driven from the LVPECL bus master, supporting synchronous sampling and sync functions across all connected boards.

# **PCI Express Interface**

The Model 52624 includes an industrystandard interface fully compliant with PCIe Gen. 1 x8 bus specifications. The interface automatically adjusts to accommodate fewer lanes, and includes dual DMA controllers for efficient transfers to and from the board.

# **Form Factor Adaptors**

All Pentek Cobalt XMC modules can be adapted to other standard embedded system form factors through the use of adaptor boards. Available versions include PCIe, 3U and 6U OpenVPX, 3U and 6U cPCI, and AMC. For more information and the Pentek's Product Selector Tool visit our website at: www.pentek.com.

# **Specifications**

Front Panel Analog Signal Inputs

Input Type: Transformer-coupled, front panel female SSMC connectors Transformer Type: Coil Craft WBC4-6TLB

**Full Scale Input:** +8 dBm into 50 ohms **3 dB Passband:** 300 kHz to 700 MHz

A/D Converters

Quantity: Two

**Type:** Texas Instruments ADS5485 **Sampling Rate:** 10 MHz to 200 MHz

**Resolution:** 16 bits

# Dual-Channel, 34-Signal Adaptive IF Relay - 3U OpenVPX

# **Model 8267**

The Model 8267 is a fully-integrated development system for Pentek Cobalt, Onyx and Flexor 3U VPX boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

## **Ordering Information**

| Model | Description            |

|-------|------------------------|

| 52624 | Dual-Channel 34-Signal |

|       | Adaptive IF Relay - 3U |

|       | OpenVPX                |

### Options:

| -064 | XC6VSX315T (required   |

|------|------------------------|

| -702 | L2 (air cooled)        |

|      | environmental level    |

| -712 | L2 (conduction cooled) |

|      | environmental level    |

| -730 | 2-slot heatsink        |

|      |                        |

Contact Pentek for availability of rugged and conduction-cooled versions

| Model | Description            |  |  |

|-------|------------------------|--|--|

| 8267  | Development System     |  |  |

|       | See 8267 Datasheet for |  |  |

|       | Options                |  |  |

### Digital Downconverters

Quantity: 34

**Decimation Range:** 512 to 8192, in steps

of 8

LO Tuning Freq. Resolution: 32 bits,

LO SFDR: >100 dB

Phase Offset: 1 bit, 0 or 180 degrees

FIR Filter: 18-bit coefficients

Output: Complex, 16-bit I + 16-bit Q Default Filter Set: 80% bandwidth, <0.3 dB passband ripple, >100 dB stopband attenuation

### **Input Gain Blocks**

Quantity: 34

**Data**: Complex, 16-bit I + 16-bit Q **Gain Range**: 16-bit Q8.8 format, approximately +/- 48 dB

# Output Gain Blocks

Quantity: 34

**Data**: Complex, 16-bit I + 16-bit Q **Gain Range**: 16-bit Q8.8 format, approximately +/- 48 dB

# **Digital Upconverters**

Quantity: 34

**Interpolation Range:** 512 to 8192, in

steps of 8

**LO Tuning Freq. Resolution:** 32 bits, 0 to  $f_s$

LO SFDR: >120 dB

FIR Filter: 18-bit coefficients, 16-bit output **Default Filter Set:** 80% bandwidth, <0.3 dB passband ripple, >100 dB stopband attenuation

#### D/A Converters

Analog Output Channels: 2 Type: Texas Instruments DAC5688 Input Data Rate: 200 MHz max.

Output Signal: Real

**Output Sampling Rate:** 800 MHz max. with 4x interpolation

**Resolution:** 16 bits

# Front Panel Analog Signal Outputs

Output: Transformer-coupled, front panel female SSMC connectors Transformer: Coil Craft WBC4-6TLB Full Scale Output: +4 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

**Sample Clock Sources:** On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

### **Clock Synthesizer**

Clock Source: Selectable from on-board programmable VCXO (10 to 810 MHz), front panel external clock or LVPECL timing bus

**Synchronization:** VCXO can be locked to an external 4 to 180 MHz PLL system reference, typically 10 MHz

Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

### **External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 10 to 800 MHz divider input clock or PLL system reference

Timing Bus: 26-pin connector LVPECL bus includes, clock/sync/gate/PPS inputs and outputs; TTL signal for gate/ trigger and sync/PPS inputs

### Field Programmable Gate Array

Required: Xilinx Virtex-6 XC6VSX315T

### **PCI-Express Interface**

PCI Express Bus: Gen. 1: x4 or x8;

# Environmental Standard:

Operating Temp: 0° to 50° C Storage Temp: –20° to 90° C Relative Humidity: 0 to 95%, non-cond.

# Option 702 L2 Extended Temp (aircooled):

Operating Temp: -20° to 65° C Storage Temp: -40° to 100° C Relative Humidity: 0 to 95%, non-cond.

# Option 712 L2 Extended Temp (conduction-cooled):

Operating Temp: -20° to 65° C Storage Temp: -40° to 100° C Relative Humidity: 0 to 95%, non-cond.

**Size:** Standard 3U VPX board, 100 x 160 mm (3.937 x 6.299 in.)

# **VPX Families**

Pentek offers two families of 3U VPX products: the 52xxx and the 53xxx. For more information on a 53xxx product, please refer to the product datasheet. The table below provides a comparison of their main features.

### **VPX Family Comparison**

|                  | 52xxx                         | 53xxx                            |  |

|------------------|-------------------------------|----------------------------------|--|

| Form Factor      | 3U VPX                        |                                  |  |

| # of XMCs        | One XMC                       |                                  |  |

| Crossbar Switch  | No                            | Yes                              |  |

| PCIe path        | VPX P1                        | VPX P1 or P2                     |  |

| PCIe width       | x4                            | x8                               |  |

| Option -104 path | 20 pairs on VPX P2            |                                  |  |

| Option -105 path | Two x4 or one x8<br>on VPX P1 | Two x4 or one x8 on VPX P1 or P2 |  |

| Lowest Power     | Yes                           | No                               |  |

| Lowest Price     | Yes                           | No                               |  |

## A/D Performance

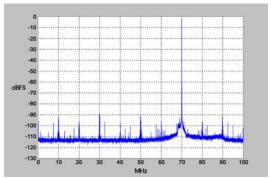

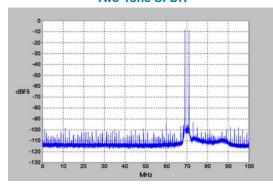

# **Spurious Free Dynamic Range**

$f_{in} = 70$  MHz,  $f_{s} = 200$  MHz, Internal Clock

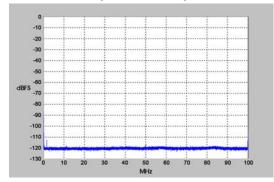

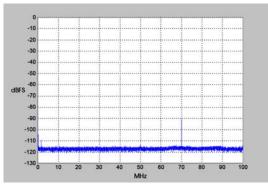

# **Spurious Pick-up**

f<sub>s</sub> = 200 MHz, Internal Clock

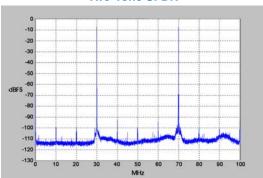

### **Two-Tone SFDR**

$f_1 = 30 \text{ MHz}, f_2 = 70 \text{ MHz}, f_s = 200 \text{ MHz}$

# **Two-Tone SFDR**

$f_1 = 69 \text{ MHz}, f_2 = 71 \text{ MHz}, f_s = 200 \text{ MHz}$

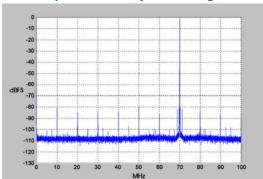

# **Adjacent Channel Crosstalk Crosstalk**

$f_{in Ch2} = 70 MHz$ ,  $f_{s} = 200 MHz$ , Ch 1 shown

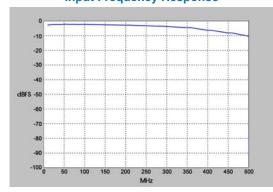

# **Input Frequency Response**

f = 200 MHz, Internal Clock

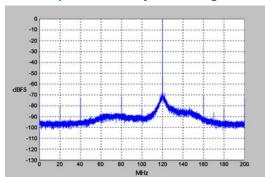

# **Spurious Free Dynamic Range**

$f_{out} = 70 \text{ MHz}, f_{s} = 200 \text{ MHz}, Internal Clock}$

## **D/A Performance**

## **Spurious Free Dynamic Range**

$\rm f_{out}$  = 140 MHz,  $\rm f_{s}$  = 400 MHz, External Clock