# **Contents**

| Xilinx FPGA Performance                                                                           | 3           |

|---------------------------------------------------------------------------------------------------|-------------|

| The Cobalt/Onyx Architecture                                                                      | 4           |

| Cobalt/Onyx Formats & Interfaces                                                                  |             |

| Support Software                                                                                  | <u>15</u>   |

| Models 71620 & 71720: Transceiver with Three A/Ds, DUC, Two D/As, Virtex-6 & Virtex-7 FPGAs - XMC | <u>16</u>   |

| Model 71621: Transceiver with Three A/Ds, DDCs, DUC, Two D/As - XMC                               |             |

| Models 71630 & 71730: 1 GHz A/D, 1 GHz D/A, Virtex-6 & Virtex-7 FPGAs - XMC                       | <u>21</u>   |

| Model 71640: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, Virtex-6 FPGA - XMC              | <u>24</u>   |

| Model 71641: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, with DDC, Virtex-6 FPGA - XMC    | 27          |

| Model 71741: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, with DDC, Virtex-6 FPGA - XMC    | 29          |

| Model 71650: Transceiver with Two A/Ds, DUC, Two D/As, Virtex-6 FPGA - XMC                        | <u>32</u>   |

| Model 71651: Transceiver with Two A/Ds, DDC, DUC, Two D/As, Virtex-6 FPGA - XMC                   | 35          |

| Model 71751: Transceiver with Two A/Ds, DDC, DUC, Two D/As, Virtex-7 FPGA - XMC                   | 37          |

| Models 71660 & 71760: 4-Channel 200 MHz A/D, Virtex-6 & Virtex-7 FPGAs - XMC                      | 40          |

| Model 71661: 4-Channel 200 MHz A/D with DDCs and Beamformer, Virtex-6 FPGA -XMC                   | <u>43</u>   |

| Model 71662: 4-Channel 200 MHz A/D with 32-Channel DDC, Virtex-6 FPGA - XMC                       | <u>45</u>   |

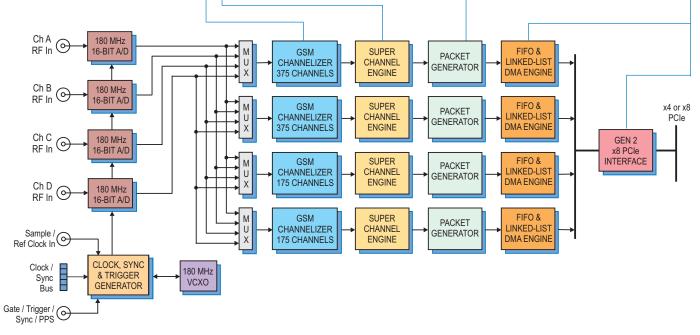

| Model 71663: 1100 GSM Channelizer with Quad 200 A/D, Virtex-6 FPGA - XMC                          | . <u>47</u> |

| Model 71670: 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - XMC                                 | . 49        |

| Model 71671: 4-Channel 1.25 GHz D/A with DUC, Extended Interpolation, Virtex-6 FPGA - XMC         | <u>52</u>   |

| Model 71771: 4-Channel 1.25 GHz D/A with DUC, Extended Interpolation, Virtex-7 FPGA - XMC         |             |

| Model 71690: L-Band RF Tuner with 2-Channel 200 MHz A/D, Virtex-6 FPGA - XMC                      |             |

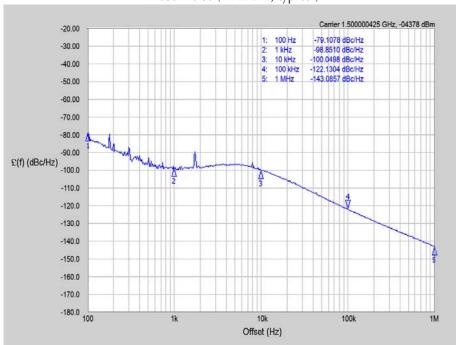

| Performance Graphs                                                                                | <u>60</u>   |

| Model 71610: LVDS Digital I/O with Virtex-6 FPGA - XMC                                            |             |

| Model 71611: Quad Serial FPDP Interface with Virtex-6 FPGA - XMC                                  | <u>64</u>   |

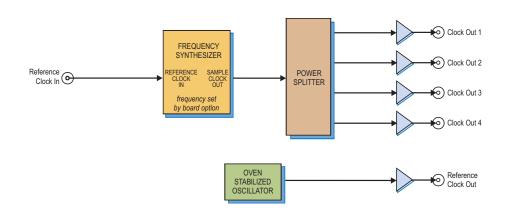

| Model 7192: High-Speed Synchronizer and Distribution Board - PMC/XMC                              | <u>66</u>   |

| Model 9192: Rackmount High-Speed System Synchronizer Unit                                         | <u>68</u>   |

| Model 7893: System Synchronizer and Distribution Board - PCIe                                     | <u>70</u>   |

| Model 7194: High-Speed Clock Generator - PMC/XMC                                                  | <u>72</u>   |

| Model 8266: PC Development System for PCIe Cobalt and Onyx Boards                                 | <u>74</u>   |

| Customer Information                                                                              | <u>7</u> 5  |

| Cobalt/Onyx Selection Chart                                                                                              |       |                         |              |                          |             |                   |

|--------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|--------------|--------------------------|-------------|-------------------|

| <b>6</b> 6alt                                                                                                            | Onyx  | A/D Convert<br>Qty Rate | ters<br>Bits | D/A Converte<br>Qty Rate | ers<br>Bits | Other<br>Features |

| 71620                                                                                                                    | 71720 | 3 200 MHz               | 16           | 2 800 MHz                | 16          |                   |

| 71621                                                                                                                    |       | 3 200 MHz               | 16           | 2 800 MHz                | 16          | 3 DDCs, Sum, Int  |

| 71660                                                                                                                    | 71760 | 4 200 MHz               | 16           |                          |             |                   |

| 71661                                                                                                                    |       | 4 200 MHz               | 16           |                          |             | 4 DDCs, Sum       |

| 71662                                                                                                                    |       | 4 200 MHz               | 16           |                          |             | 32 DDCs, Sum      |

| 71663                                                                                                                    |       | 4 200 MHz               | 16           |                          |             | 1100 DDCs         |

| 71690                                                                                                                    | 71790 | 2 200 MHz               | 16           |                          |             | L-Band Tuner      |

| 71650                                                                                                                    |       | 2 400 MHz               | 14           | 2 800 MHz                | 16          |                   |

| 71651                                                                                                                    | 71751 | 2 400 MHz               | 14           | 2 800 MHz                | 16          | 2 DDCs, Int       |

| 71650                                                                                                                    |       | 2 500 MHz               | 12           | 2 800 MHz                | 16          |                   |

| 71651                                                                                                                    | 71751 | 2 500 MHz               | 12           | 2 800 MHz                | 16          | 2 DDCs, Int       |

| 71630                                                                                                                    | 71730 | 1 1 GHz                 | 12           | 1 1 GHz                  | 12          |                   |

| 71640                                                                                                                    |       | 1/2 3.6/1.8 GH          | z 12         |                          |             |                   |

| 71641                                                                                                                    | 71741 | 1/2 3.6/1.8 GH          | z 12         |                          |             | 1/2 DDCs,         |

| 71670                                                                                                                    |       |                         |              | 4 1.25 GHz               | 16          |                   |

| 71671                                                                                                                    | 71771 |                         |              | 4 1.25 GHz               | 16          | Extended Int      |

| 71610                                                                                                                    |       |                         |              |                          |             | LVDS I/O          |

| 71611                                                                                                                    |       |                         |              |                          |             | Quad sFPDP        |

| Rate = Maximum Sampling Frequency DDC = Digital Downconverter Int = Interpolation Filter SFPDP = Serial FPDP - VITA 17.1 |       |                         |              |                          |             |                   |

Sum = Beamforming Summation Block & Aurora Chaining Interface

## Xilinx FPGA Performance

# The Latest Generations of Virtex FPGAs

With each new generation of FPGA devices, Xilinx continues to push the performance envelope to match the ever increasing requirements of target applications.

The announcement of the Virtex-6 and Virtex-7 were no exception. More processing power, lower power consumption, and updated interface features to match the latest technology I/O requirements, are all part of these new devices.

While it might be easy to assume that faster, bigger, more powerful is better, it's important to understand how the latest FPGA innovations actually deliver this higher performance to best match the device to the specific requirements of the application.

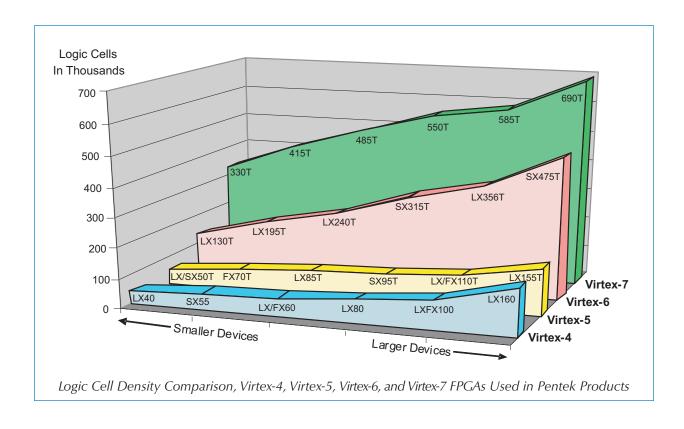

One of the standard metrics for FPGAs is the number of logic cells. This figure shows the steady improvement in the last four generations of

Xilinx FPGAs starting with the Virtex-4 and continuing to the Virtex-7. The graph displays the number of logic cells contained in a range of different density devices offered in a 35 mm x 35 mm BGA (Ball-Grid Array) package. This clearly shows the dramatic increase in resource density, bounded by the constraints of the size and power dissipation capacity of a given package.

Since Virtex-4 CLBs (Configurable Logic Blocks) comprise eight logic cells, while Virtex-5 and Virtex-6 CLBs comprise 12, the increase in logic cells between Virtex-4 and Virtex-5 actually translates to a decrease in CLBs because each CLB in the Virtex-5 requires more logic cells. While the Virtex-5 CLBs are more powerful than their Virtex-4 counterparts, there are still fewer of them to use. What is also clear from this graph is that the Virtex-6 represents a signifi-

cant increase in density from the Virtex-5 family.

The Virtex-7 offers the highest performance thus far with twice the performance and twice the resources of the Virtex-6.

The Virtex-7 devices feature low-power 28 nm process technology to implement up to 3.1 Tbits/sec of I/O and up to 2 million logic cells. They provide up to 6.7 TMACs of DSP resources, especially important for software radio applications. Because of new process technologies and other power management schemes, they consume half the power of Virtex-6 for a given function.

This combination of lower power and higher performance for each of the key resources benefits software radio, opens up new product markets, and extends the capabilities of existing applications.

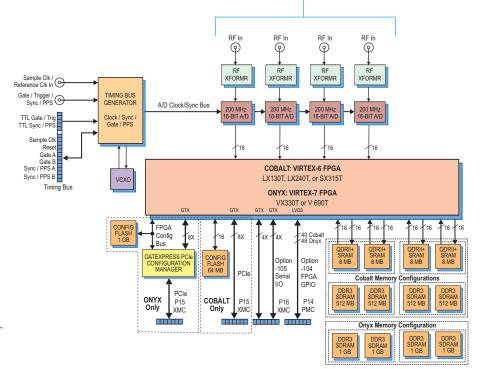

# Features and Implementation

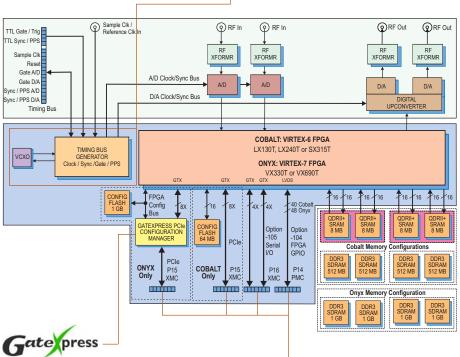

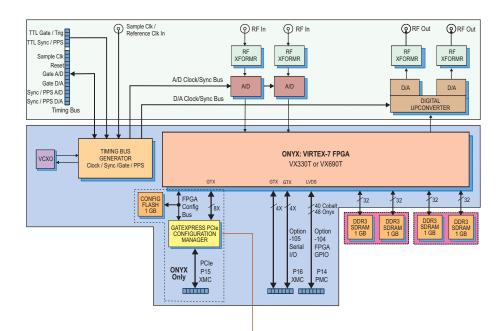

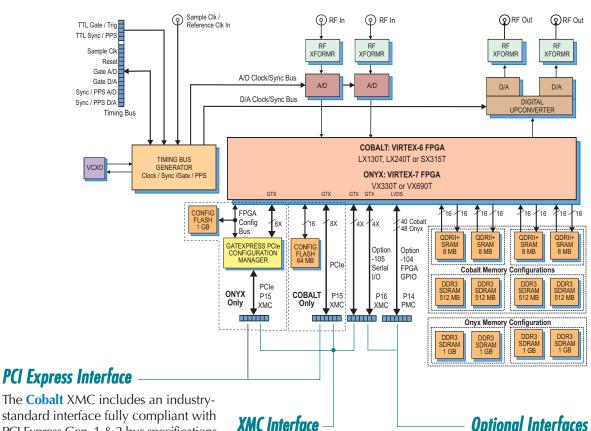

## **Cobalt & Onyx Architectural Features**

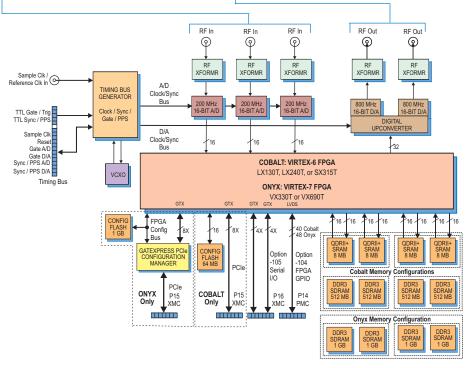

- Cobalt®: Xilinx Virtex-6 FPGA

- Onyx®: Xilinx Virtex-7 FPGA

- Configurable memory resources depending on model

- On-board clocking and synchronization

- Modular I/O design to support a wide range of signal types

## **Cobalt & Onyx Performance Features**

- A/D sampling rates from 10 MHz to 3.6 GHz

- D/A sampling rates up to 1.25 GHz

- Powerful linked-list DMA engines

- PCI Express as the primary control and data transfer interface

- Secondary serial gigabit interface

- All models available in XMC, PCI Express, OpenVPX and CompactPCI formats

- Available in commercial and in several ruggedization levels up to and including conduction cooling

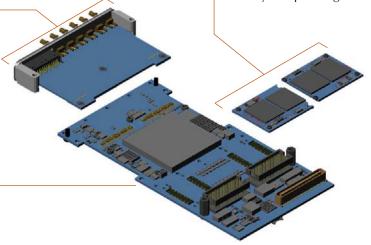

## These two smaller

These two smaller boards are used for the memory resources allowing for customization of two types of memory—depending on model.

-Memory Resources

## I/O Module

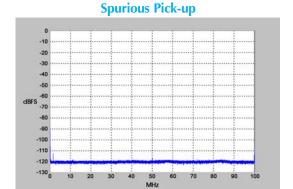

The I/O module is a separate printedcircuit board that caries all of the analog interface circuitry providing excellent isolation from noise. Typical front panel signals include analog in and out, clocking, sync, and triggering.

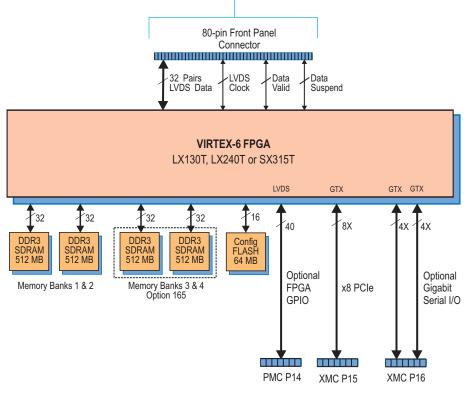

The main board serves as the foundation of all Cobalt and Onyx products. It houses the FPGA, FLASH memory, XMC interfaces, user programmable FPGA interfaces and hosts the memory and I/O modules.

### Flexible Architecture

The modularity of this assembly offers an unprecedented degree of flexibility for creating Cobalt or Onyx modules with completely different features by just incorporating different I/O modules.

As shown in the diagram, the front panel allows for a maximum of six

SSMC signal connectors. The external clocking, trigger and synchronization connector is a front-panel multipin flat cable connector and is the same on all models, except those designed to operate at frequencies higher than 1.0 GHz.

# **Components and Circuitry**

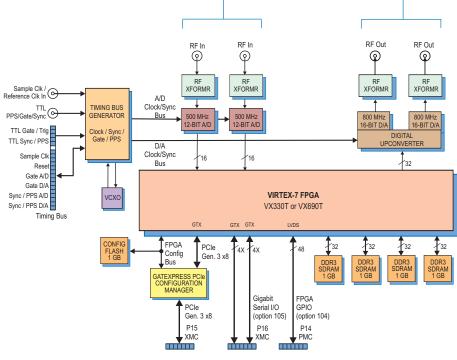

## **Cobalt or Onyx I/O Module**

Shown here is a typical Cobalt or Onyx I/O module. The input analog ports are transformer-coupled to two high-speed A/D converters. The digital outputs are delivered into the Virtex-6 or Virtex-7 FPGA for signal processing, data capture or for routing to other module resources.

Besides the two A/Ds, the typical module could include one DUC (Digital Upconverter), and two D/As which are transformer-coupled to the output analog ports.

In addition to the input and output ports, the module includes a multiport connector for clocking and synchronization. All connectors are on the front panel.

FLASH Memory —

Cobalt: The 16-bit wide 64 MB FLASH provides non-volatile memory for factory boot code, self-test, and user parameters Onyx: The 16-bit wide 1024 MB FLASH provides non-volatile memory for factory boot code, self-test, user parameters, and FPGA images for dynamically reconfiguring the FPGA.

## **Memory Resources**

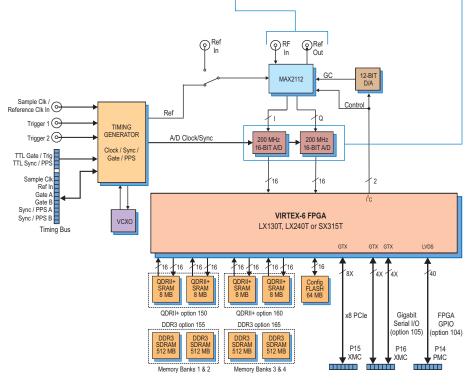

**Cobalt:** Up to four independent memory banks can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each memory type.

Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the board's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep.

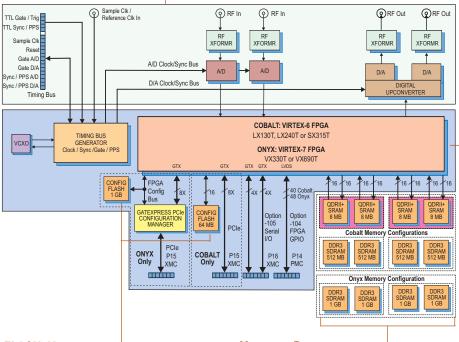

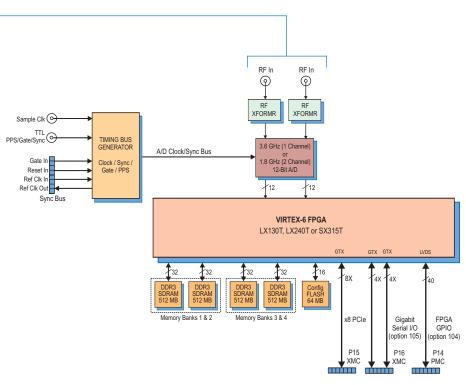

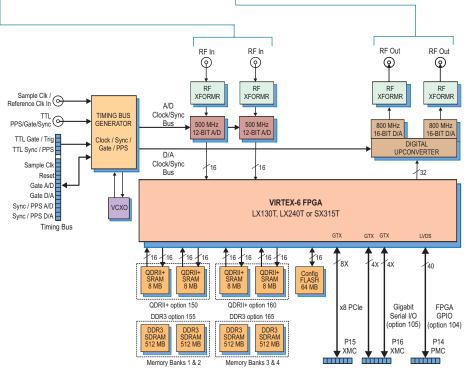

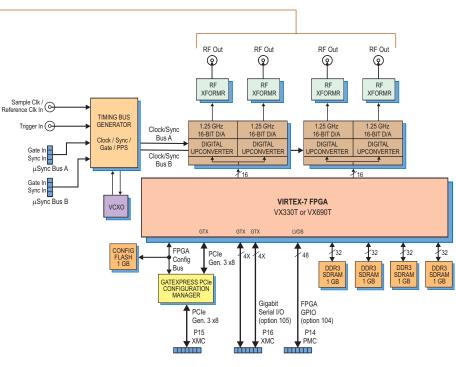

## Xilinx Virtex-6 or Virtex-7 FPGA

The Cobalt Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T.

The Onyx Virtex-7 FPGA site can be populated with one of two FPGAs to match the specific requirements of the processing task. Supported FPGAs are: VX330T or VX690T.

The SX315T features 1344 DSP48E slices, while the VX690T features 3600 DSP48E1 slices. These devices are ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception.

Onyx: Four independent DDR3 SDRAM memory banks are available. Each bank is 1 GB deep and is an integral part of the board's DMA capabilities, providing FIFO memory space for creating DMA packets. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes.

More on next page >

# **Components and Circuitry**

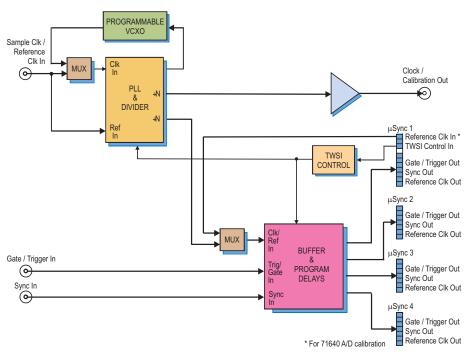

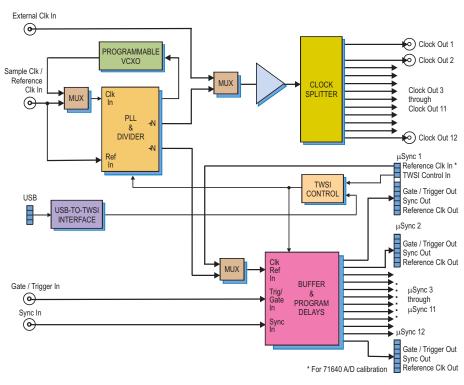

## Clocking and Synchronization

The internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

The timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives an external sample clock which can be used directly for either the A/D or D/A sections or can be divided by a built-in clock synthesizer circuit to provide different A/D and D/A clocks.

In an alternate mode, the sample clock can be sourced from an onboard

programmable VCXO (Voltage-Controlled Crystal Oscillator). In this mode, the synthesizer locks the VCXO to an external system reference, typically 10 MHz.

A front panel 26-pin LVPECL Clock/ Sync connector allows multiple boards to be synchronized. In the slave mode, it accepts LVPECL inputs that drive the clock, sync and gate signals. In the master mode, the LVPECL bus can drive the timing signals for synchronizing multiple boards.

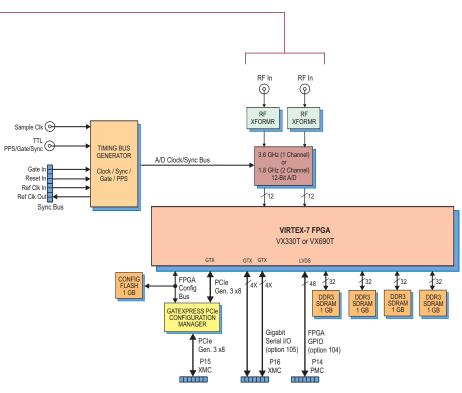

Available only in the **Onyx** series, the GateXpress<sup>TM</sup> is a sophisticated FPGA PCle configuration manager for loading and reloading the FPGA. At powerup, GateXpress presents a PCle target for the host computer to discover, effectively giving the FPGA time to load from FLASH. This is especially important for larger FPGAs where the loading times can exceed the PCle discovery window.

The board's configuration FLASH can hold up to four FPGA images for dynamically reconfiguring the FPGA.

## **Board Interfaces**

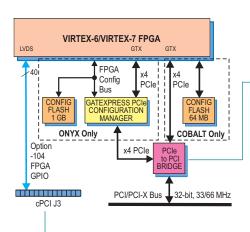

The FPGA is also used to implement the primary board interfaces. The basic XMC module shown here is also available in different formats, such as PCI Express, OpenVPX, and CompactPCI.

More information about formats and interfaces starts on page 9.

## **GateXpress for FPGA Configuration**

The Onyx architecture includes GateXpress, a sophisticated FPGA-PCle configuration manager for loading and reloading the FPGA. At power up, GateXpress immediately presents a PCle target for the host computer to discover, effectively giving the FPGA time to load from FLASH.

This is especially important for larger FPGAs where the loading times can exceed the PCIe discovery window, typically 100 msec on most PCs.

The board's configuration FLASH can hold four FPGA images. Images can be factory-installed IP or custom IP created by the user, and programmed into the FLASH via JTAG using Xilinx iMPACT or through the board's PCIe

interface. At power up the user can choose which image will load based on a hardware switch setting.

Once booted, GateXpress allows the user three options for dynamically reconfiguring the FPGA with a new IP image. The first is the option to load an alternate image from FLASH through software control. The user selects the desired image and issues a reload command.

The second option is for applications where the FPGA image must be loaded directly through the PCIe interface. This is important in security situations where there can be no latent user image left in nonvolatile memory when power is removed. In applications where the

FPGA IP may need to change many times during the course of a mission, images can be stored on the host computer and loaded through PCle as needed.

The third option, typically used during development, allows the user to directly load the FPGA through JTAG using Xilinx iMPACT.

In all three FPGA loading scenarios, GateXpress handles the hardware negotiation simplifying and streamlining the loading task. In addition, GateXpress preserves the PCle configuration space allowing dynamic FPGA reconfiguration without needing to reset the host computer to rediscover the board. After the reload, the host simply continues to see the board with the expected device ID.

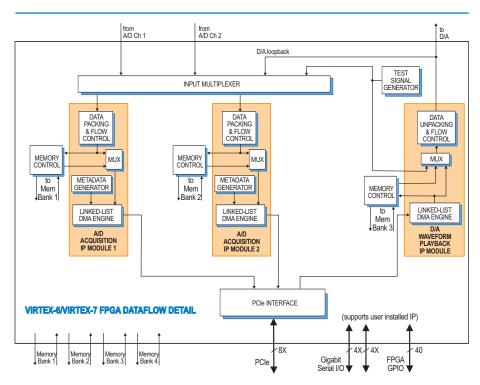

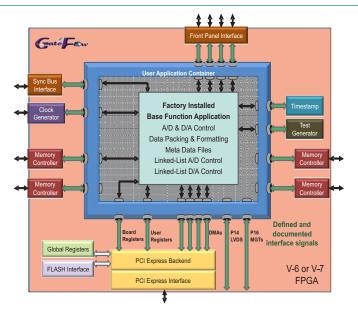

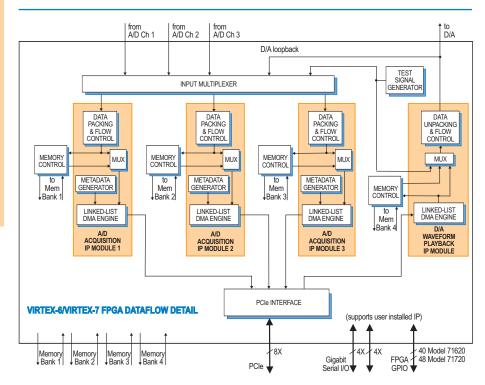

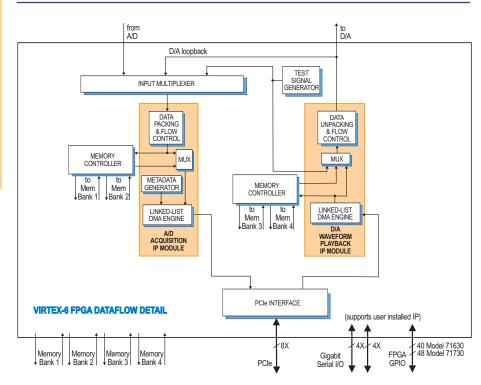

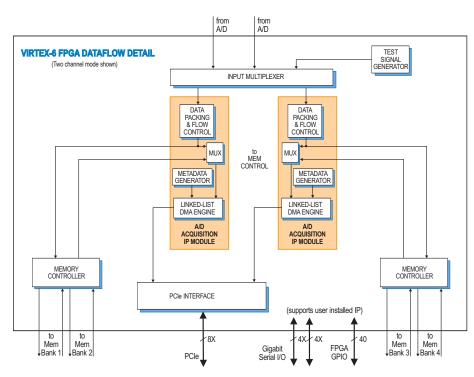

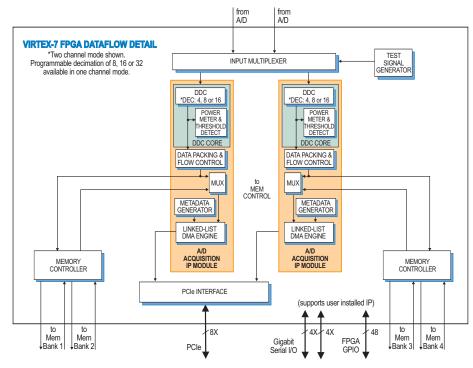

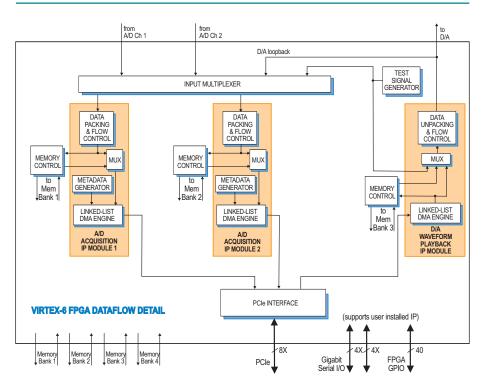

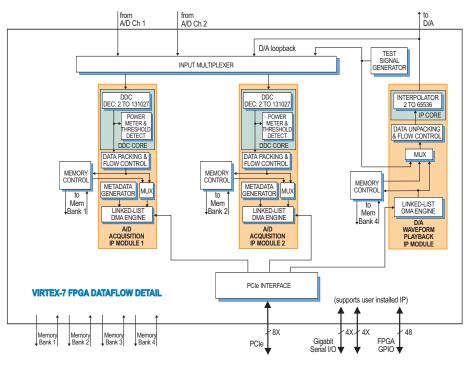

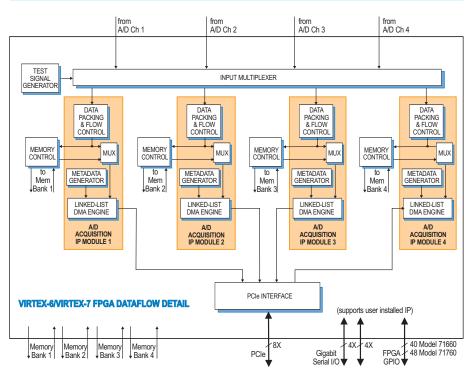

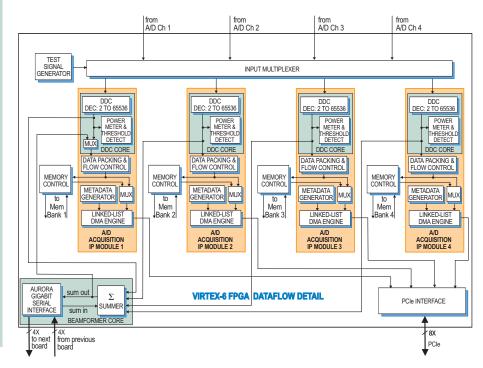

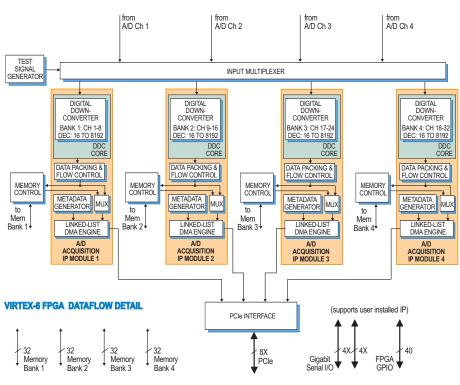

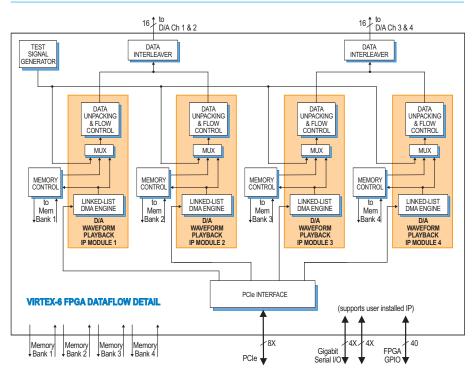

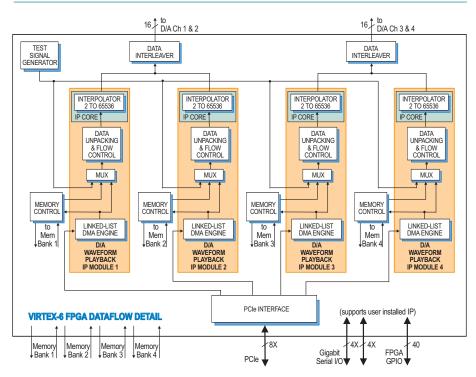

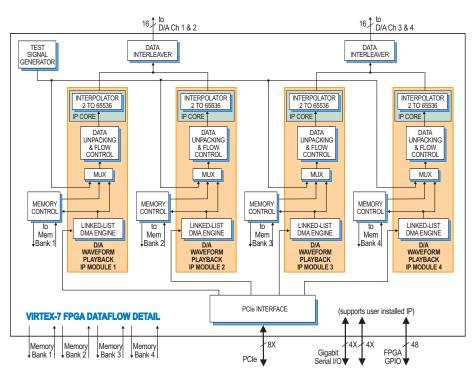

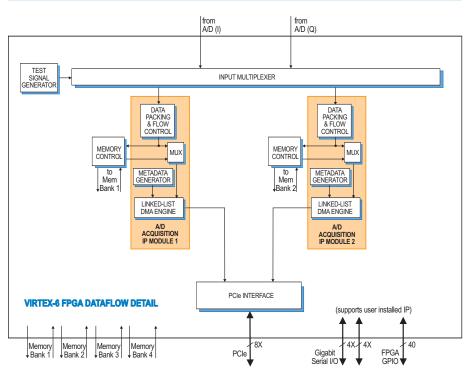

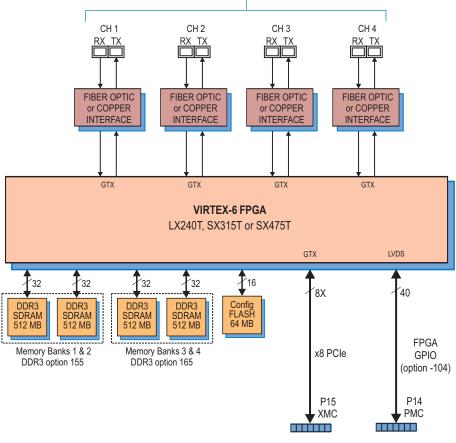

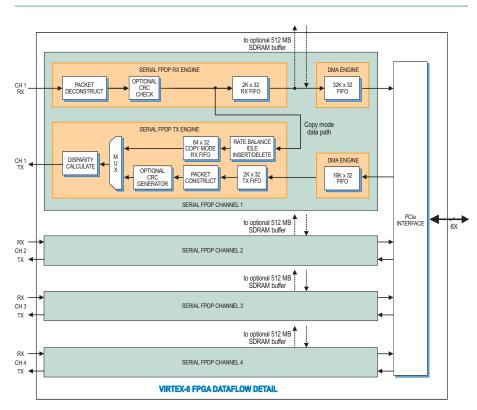

# FPGA Dataflow

All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering, and memory control. The Cobalt & Onyx Architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt/Onyx family is delivered with factory-installed

applications ideally matched to the board's analog interfaces. Depending on model, the factory-installed functions may include A/D acquisition and D/A waveform playback IP modules. IP modules for either DDR3 or QDRII+ (Cobalt only) memories, a controller for all data clocking and synchronization functions, a test signal generator, and a PCIe interface complete the factoryinstalled functions and enable the board to operate as a complete turnkey solution without the need to develop any FPGA IP.

For applications that require specialized functions, users can install custom IP for data processing. Pentek GateFlow® FPGA Design Kits (described later in this catalog) include all of the factory installed modules as documented source code. Developers can integrate their IP with the Pentek factory-installed functions or use the GateFlow to completely replace the Pentek IP with theirs.

## A/D Acquisition IP Modules

This typical Cobalt/Onyx module includes two A/D Acquisition IP modules for easy capture and data moving. Each IP module can receive data from either of the two A/Ds, a test signal generator or from the D/A Waveform Playback IP Module in loopback mode. Each IP module has an associated memory bank for buffering data in FIFO mode or for storing data in transient capture mode. All memory banks are supported with DMA engines for moving A/D data through the PCIe interface.

These powerful linked-list DMA engines are capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing A/D channel ID, a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

## D/A Waveform Playback IP Module

Factory-installed functions for this typical Cobalt/Onyx module include a sophisticated D/A Waveform Playback IP module. A linked-list controller allows users to easily play back waveforms stored in either on-board memory or off-board host memory to the dual D/As.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

## XMC Format

Here is a photograph of the typical board reviewed in detail in the previous section. In its XMC configuration, each Cobalt or Onyx module complies with the VITA 42.0 XMC specification and is suitable for mounting on motherboards with PMC/XMC connectors.

All XMC modules are available in commercial and in several ruggedization levels up to and including conduction

The XMC format applies to the Model 71xxx product family.

The Cobalt XMC includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Gen. 2 provides 4 GB/sec peak data transfer rate.

The **Onyx** XMC includes an industrystandard interface fully compliant with PCI Express Gen. 1, 2 & 3 bus specifications. Gen. 3 provides 8 GB/sec peak transfer rate.

The x8 interface includes multiple DMA controllers for efficient transfers to and from the module.

Both Cobalt and Onyx XMC products comply with the VITA 42.0 XMC specification. Each of the two connectors provides dual 4X links or a single 8X link.

With dual XMC connectors, the XMC products support both x4 and x8 PCle on the first XMC connector leaving the second connector free to support userinstalled transfer protocols specific to the target application.

## **Optional Interfaces**

Option -104 installs the P14 PMC connector with 20 pairs of LVDS connections (Cobalt) or 24 pairs (Onyx) to the FPGA for custom I/O.

Option -105 installs the P16 XMC connector with a single 8X or dual 4X gigabit links to the FPGA to support serial protocols.

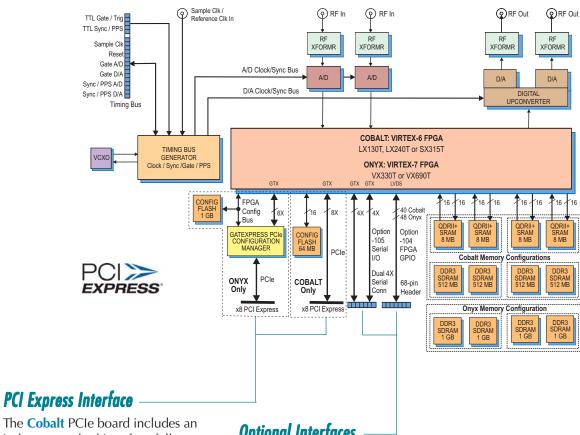

# **PCI Express Format**

The PCI Express format shown here is suitable for mounting in PCs with PCle connectors and interfaces. Physically, the XMC module reviewed in the previous page is mounted on a PCI Express "carrier" board with x8 PCIe motherboard connectors. Other connectors provide additional interfaces as described below.

The unique design of the PCIe carrier includes an integrated fan that keeps the module cool even in demanding situations while still requiring a single PCle slot.

The Cobalt PCIe board includes an industry-standard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Gen. 2 provides 4 GB/sec peak data transfer rate.

The **Onyx** PCIe board includes an industry-standard interface fully compliant with PCI Express Gen. 1, 2 & 3 bus specifications. Gen. 3 provides 8 GB/sec peak transfer rate.

The x8 interface includes multiple DMA controllers for efficient transfers to and from the module.

## **Optional Interfaces**

Option -104 connects 20 pairs of LVDS connections (Cobalt) or 24 pairs (Onyx) from the FPGA on PMC P14 to a 68-pin DIL ribbon-cable header on the PCIe board for custom I/O.

Option -105 connects two 4X gigabit serial links from the FPGA on XMC P16 to two 4X gigabit serial connectors along the top edge of the PCIe board.

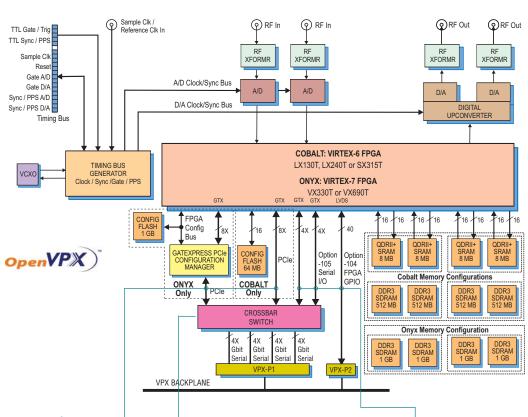

# 3U OpenVPX Format 1

The OpenVPX Format 1 is compatible with several VITA standards including: VITA-46, VITA-48 and VITA-65 (OpenVPX<sup>TM</sup> System Specification)

Shown here is the 3U OpenVPX COTS version (left) and the rugged version which is available in several ruggedization levels up to and including conduction cooling.

Another OpenVPX format is described in the next page.

## **PCI Express Interface**

The Cobalt 3U OpenVPX board includes an industry-standard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Gen. 2 provides 4 GB/sec peak data transfer rate.

The **Onyx** 3U OpenVPX board includes an industry-standard interface fully compliant with PCI Express Gen. 1, 2 & 3 bus specifications. Gen. 3 provides 8 GB/sec peak transfer rate.

The x8 interface includes multiple DMA controllers for efficient transfers to and from the board.

## - Fabric-Transparent Crossbar Switch

The 3U OpenVPX Cobalt or Onyx board features a unique high-speed switching configuration. A fabric-transparent crossbar switch bridges numerous interfaces and components on the board using gigabit serial data paths with no latency.

Programmable signal input equalization and output pre-emphasis settings enable optimization. Data paths can be selected as single (1X) lanes, or groups of four lanes (4X) for routing over to the VPX-P1 connector.

## **Optional Interfaces**

Option -104 provides 20 pairs of LVDS connections between the FPGA and the VPX-P2 connector for custom I/O.

Option -105 connects two 4X gigabit serial links from the FPGA on XMC P16 to the crossbar switch for routing to VPX-P1.

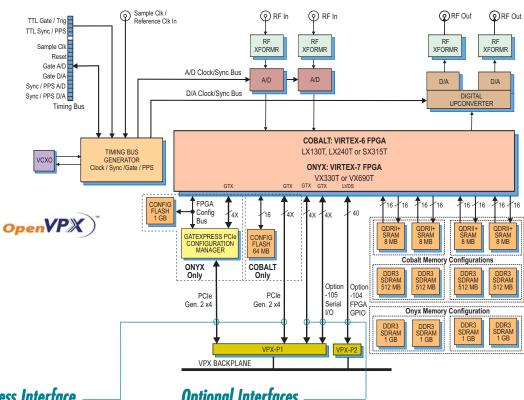

# 3U OpenVPX Format 2

The OpenVPX Format 2 is compatible with several VITA standards including: VITA-46, VITA-48 and VITA-65 (OpenVPX<sup>TM</sup> System Specification)

Shown here is the 3U OpenVPX COTS version (left) and the rugged version which is available in several ruggedization levels up to and including conduction cooling.

A comparison of the two OpenVPX formats is given in the table below.

## **PCI Express Interface**

Both Cobalt and Onyx boards include an industry-standard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications.

The x4 PCle interface includes multiple DMA controllers for efficient transfers to and from the board.

## **Optional Interfaces**

Option -104 installs 20 pairs of LVDS connections (Cobalt) or 24 pairs (Onyx) between the FPGA and VPX-P2 for custom I/O.

Option -105 connects two 4X gigabit serial links from the FPGA to VPX-P1 to support serial protocols.

## **OpenVPX Families**

By omitting the Format 1 Crossbar switch, Format 2 products achieve significant reductions in power and price. These and other differences are shown in the comparison table.

### **OpenVPX Family Comparison**

|                  | Format 2                      | Format 1                         |  |

|------------------|-------------------------------|----------------------------------|--|

| Form Factor      | 3U OpenVPX                    |                                  |  |

| # of XMCs        | One XMC                       |                                  |  |

| Crossbar Switch  | No                            | Yes                              |  |

| PCle path        | VPX P1                        | VPX P1 or P2                     |  |

| PCIe width       | x4                            | x8                               |  |

| Option -104 path | 24 pairs on VPX P2            | 20 pairs on VPX P2               |  |

| Option -105 path | Two x4 or one x8<br>on VPX P1 | Two x4 or one x8 on VPX P1 or P2 |  |

| Lowest Power     | Yes                           | No                               |  |

| Lowest Price     | Yes                           | No                               |  |

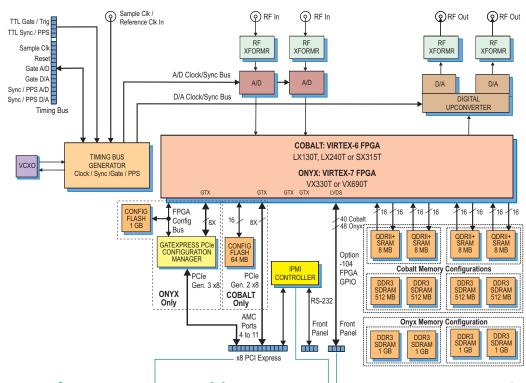

# **AMC Format**

## **Module Management**

The AMC format complies with the AMC.1 specification by providing an x8 PCle connection to AdvancedTCA carriers or µTCA chassis. Module management is provided by an IPMI 2.0 MMC (Module Management Controller).

## **PCI Express Interface**

The **Cobalt** AMC module includes an industry-standard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications.

The x8 PCIe interface includes multiple DMA controllers for efficient transfers to and from the board.

The **Onyx** AMC module includes an industry-standard interface fully compliant with PCI Express Gen. 1, 2 & 3 bus specifications.

The x8 PCIe interface includes multiple DMA controllers for efficient transfers to and from the board.

## Module Management

The Module Management Controller complies with the IPMI 2.0 MMC specification.

# **Optional Interface**Option -104 installs a f

Option -104 installs a front panel connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

# **CompactPCI Formats**

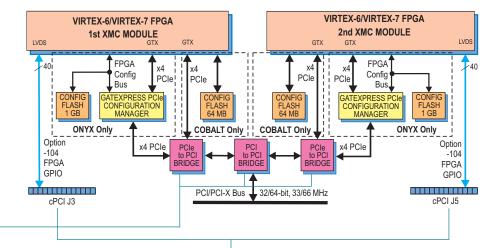

As shown here, the CompactPCI format is available in three configurations:

- 6U cPCI with double density; this configuration mounts two XMC modules on a 6U carrier board.

- 6U cPCI with single density; this configuration mounts only one XMC module on a 6U carrier board.

- 3U cPCI mounts one XMC module on a 3U carrier board

In order to describe these three configurations in more detail, we have omitted the components and circuitry shown in the previous three formats; we just show the Virtex-6/Virtex-7 FPGAs with the external connections that define the standard and optional interfaces.

## **6U cPCI Double Density**

Two PCIe-to-PCI bridges connect the x4 PCIe interfaces from each XMC module to a PCI-to-PCI bridge. This bridge connects both modules to the 32- or 64-bit, 33/66 MHz PCI/PCI-X bus.

## **6U cPCI Optional Interface**

Option -104 provides 20 pairs of LVDS connections between the FPGA and the I3 connector for custom I/O.

The J5 connector supports Option -104 for the 2nd XMC module.

## **6U cPCI Single Density**

The 2nd XMC module, its associated PCIe-to-PCI bridge, and the optional interface connection to J5 are not present.

## **3U cPCI Single Density**

A PCIe-to-PCI bridge connects the x4 PCIe interface from the XMC module to the 32-bit, 33/66 MHz PCI/PCI-X bus.

## **3U cPCI Optional Interface**

Option -104 provides 20 pairs of LVDS connections between the FPGA and the J3 connector for custom I/O.

# **Support Software**

# Pentek ReadyFlow Board Support Package

Users of high-performance data acquisition and signal processing boards often find themselves frustrated by the fact that when their new devices are delivered, they are unable to put them to immediate use.

To address this issue, Pentek has developed the **ReadyFlow**® BSPs (Board Support Packages) for all of its board-level products.

The package contains C-language examples that demonstrate the capabilities of Pentek products. The examples included provide the answers to most of the questions that occur with first-time users of these products.

ReadyFlow BSPs are designed to reduce development time during the initial stages and when new hardware is added to the system. All packages are built with a consistent style and functionnaming convention. Similar parameters on different boards have similar function calls, thereby allowing immediate familiarity with new hardware.

### Command Line Interface

The Command Line Interface is a precompiled executable that runs the hardware right out of the box, without the need to write any code.

Specific to the hardware features of the supported board, it allows operating arguments to be entered on the

command line for controlling board parameters.

For command line functions that control data acquisition, the captured data can be saved in a host file or routed to the Signal Analyzer.

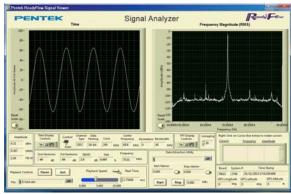

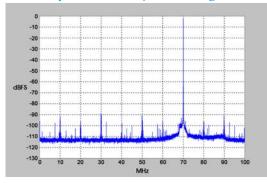

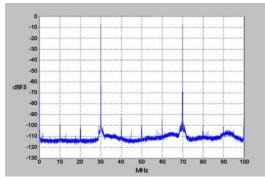

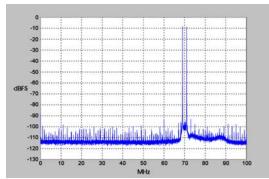

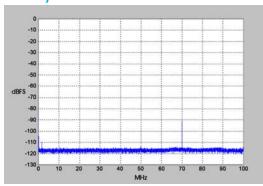

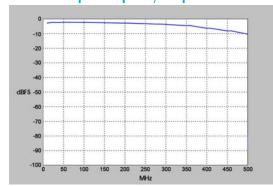

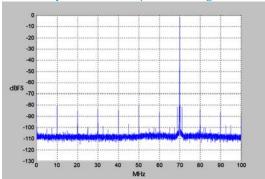

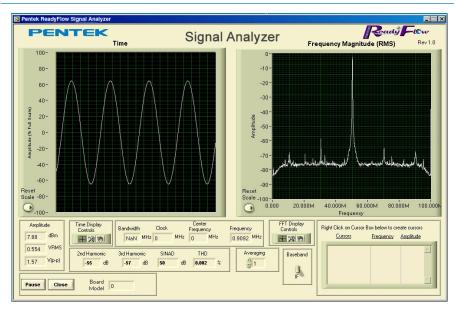

## Signal Analyzer

When used with the Command Line Interface, the Signal Analyzer allows users

to immediately start acquiring and displaying A/D data. A full-featured analysis tool, the Signal Analyzer displays data in time and frequency domains. Built-in measurement functions display 2nd and 3rd harmonics, THD (total harmonic distortion), and SINAD (signal to noise and distortion). Interactive cursors allow users to mark data points and instantly calculate amplitude and frequency of displayed signals.

# Pentek GateFlow FPGA Design Kit

## Using the FPGA Design Kit

The **GateFlow**® FPGA Design Kit allows the user to modify, replace and extend the standard factory-installed functions in the FPGA to incorporate special modes of operation, new control structures, and specialized signal-processing algorithms.

The Cobalt or Onyx architecture configures the FPGA with standard factory-supplied interfaces including memory controllers, DMA engines, A/D and D/A interfaces, timing and synchronization structures, triggering and gating logic, time stamping and header tagging, data formatting engines, and the PCle interface. These resources are connected to the User Application Container using well-defined ports that present easy-to-use data and control signals, effectively abstracting the lower level details of the hardware.

## The User Application Container

Shown here is the FPGA block diagram of a typical Cobalt/Onyx module. The User Application Container holds a collection of different factory-installed

IP modules connected to the various interfaces through the standard ports surrounding the container. The specific IP modules for each product are described in further detail in the following pages.

The GateFlow Design Kit provides a complete Xilinx ISE Foundation Tool project folder containing all the files

necessary for the developer to recompile the entire project with or without any required changes. VHDL source code for each IP module provides excellent examples of how the IP modules work, how they might be modified, and how they might be replaced with custom IP to implement a specific function.

# Models 71620 & 71720: Transceiver with Three A/Ds, DUC, Two D/As - XMC

Model 71620

Model 71620 is a member of the **Cobalt** family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. Model 71720 is a member of the **Onyx** family of high-performance modules based on the Virtex-7 FPGA.

These multichannel, high-speed data converters, are suitable for connection to HF or IF ports of a communications or radar system. Their built-in data capture and playback features offer an ideal turnkey solution.

Each model includes three A/Ds, one DUC, two D/As and four banks of memory. In addition to supporting PCI Express as a native interface, these models include general-purpose and gigabit serial connectors for application-specific I/O.

Model 71720

## Digital Upconverter and D/As

A TI DAC5688 DUC (digital upconverter) and D/A accepts a baseband real or complex data stream from the FPGA which is optionally interpolated, upconverted and then delivered to the two D/As.

When operating as a DUC, it interpolates and translates real or complex baseband input signals to any IF center frequency up to 360 MHz. It delivers real or quadrature (I+Q) digital outputs to the dual 16-bit D/A converter. Analog output is through a pair of front panel SSMC connectors.

If translation is disabled, the DAC5688 acts as a dual interpolating 16-bit D/A with output sampling rates up to 800 MHz. In both modes the DAC5688 provides interpolation factors of 2x, 4x and 8x.

### **Features**

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT or Virtex-7 VXT FPGAs

- Model 71720: GateXpress supports dynamic FPGA reconfiguration across PCIe

- Three 200 MHz 16-bit A/Ds

- One digital upconverter

- Two 800 MHz 16-bit D/As

- Model 71620: Up to 2 GB of DDR3 SDRAM or 32 MB of QDRII+ SRAM; Model 71720: 4 GB of DDR3 SDRAM

- Sample clock synchronization to an external system reference

- LVPECL clock/sync bus for multimodule synchronization

- Model 71620: PCI Express (Gen. 1 & 2) interface up to x8; Model 71720: PCI Express (Gen. 1, 2, and 3) interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

Contact Pentek for availability of rugged and conduction-cooled versions

### A/D Converters

The front end accepts three full-scale analog HF or IF inputs on front panel SSMC connectors at +8 dBm into 50 ohms with transformer coupling into three Texas Instruments ADS5485 200 MHz, 16-bit A/D converters.

The digital outputs are delivered into the Virtex-6 or Virtex-7 FPGA for signal processing, data capture or for routing to other module resources.

# Models 71620 & 71720: Transceiver with Three A/Ds, DUC, Two D/As - XMC

### Installed IP Modules

The factory-installed functions in both models include three A/D acquisition and a D/A waveform playback IP modules, ideally matched to the board's analog interfaces.

IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator, and a PCIe interface complete the factoryinstalled functions and enable these models to operate as complete turnkey solutions, without the need to develop any FPGA IP.

## A/D Acquisition IP Modules

Both models feature three A/D Acquisition IP Modules for easily capturing and moving data. Each module can receive data from any of the three A/Ds, a test signal generator or from the D/A Waveform Playback IP Module in loopback mode.

Each IP module has an associated memory bank for buffering data in FIFO mode or for storing data in transient capture mode. All memory banks are supported with DMA engines for easily moving A/D data through the PCIe interface.

These powerful linked-list DMA engines are capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing A/D channel ID, a sample-accurate time stamp and data length information. These actions simplify the host processor's job of identifying and executing on the data.

## D/A Waveform Playback IP Module

The factory-installed functions in both models include a sophisticated D/A Waveform Playback IP module. A linked-list controller allows users to easily play back to the dual D/As waveforms stored in either on-board memory or off-board host memory.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

# Models 71620 & 71720: Transceiver with Three A/Ds, DUC, Two D/As - XMC

## Also Available

| Model | Format                   |

|-------|--------------------------|

| 78620 | x8 PCI Express           |

| 53620 | 3U OpenVPX - Format 1    |

| 52620 | 3U OpenVPX - Format 2    |

| 56620 | AMC                      |

| 73620 | 3U cPCI - Single Density |

| 72620 | 6U cPCI - Single Density |

| 74620 | 6U cPCI - Double Density |

|       |                          |

| Model | Format                   |

|-------|--------------------------|

| 78720 | x8 PCI Express           |

| 53720 | 3U OpenVPX - Format 1    |

| 52720 | 3U OpenVPX - Format 2    |

| 56720 | AMC                      |

| 73720 | 3U cPCI - Single Density |

| 72720 | 6U cPCI - Single Density |

| 74720 | 6U cPCI - Double Density |

|       |                          |

## **Specifications**

Front Panel Analog Signal Inputs

Input Type: Transformer-coupled,

front panel female SSMC connectors

Transformer Type: Coil Craft

WBC4-6TLB

Full Scale Input: +8 dBm into

50 ohms

3 dB Passband: 300 kHz to 700 MHz

A/D Converters

**Type:** Texas Instruments ADS5485 **Sampling Rate:** 10 MHz to 200 MHz

Resolution: 16 bits

**D/A Converters**

Type: Texas Instruments DAC5688 Input Data Rate: 250 MHz max. Output IF: DC to 400 MHz max. Output Signal: 2-channel real or 1-channel with frequency translation Output Sampling Rate: 800 MHz

max. with interpolation **Resolution**: 16 bits

Front Panel Analog Signal Outputs

**Output Type:** Transformer-coupled, front panel female SSMC connectors

**Transformer Type:** Coil Craft

WBC4-6TLB

Full Scale Output: +4 dBm into

50 ohms

**3 dB Passband:** 300 kHz to 700 MHz **Sample Clock Sources:** On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

**Clock Synthesizer**

Clock Source: Selectable from onboard programmable VCXO (10 to 810 MHz), front panel external clock or LVPECL timing bus Synchronization: VCXO can be locked to an external 4 to 180 MHz PLL system reference, typically 10 MHz Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

**External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 10 to 800 MHz divider input clock or PLL system reference

**Timing Bus:** 26-pin connector LVPECL bus includes, clock/sync/gate/PPS inputs and outputs; TTL signal for gate/trigger and sync/PPS inputs

Model 71620 Xilinx Virtex-6 FPGA

**Standard:** CXC6VLX130T **Optional:** XC6VLX240T, or

XC6VSX315T

Model 71720 Xilinx Virtex-7 FPGA

**Standard:** XC7VX330T-2 **Optional:** XC7VX690T-2

Custom I/O

**Option -104:** Installs the PMC P14 connector with 20 LVDS pairs (Model 71620) or 24 pairs (Model 71720) to the FPGA

**Option -105:** Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the

FPGA

Memory

Model 71620

**Option 150 or 160:** Two 8 MB QDRII+ SRAM memory banks,

400 MHz DDR

**Option 155 or 165:** Two 512 MB DDR3 SDRAM memory banks,

400 MHz DDR **Model 71720**

Type: DDR3 SDRAM

Size: Four banks, 1 GB each

**PCI-Express Interface**

Model 71620

**PCI Express Bus:** Gen. 1: x4 or x8; Gen. 2: x4

Model 71720

**PCI Express Bus:** Gen. 1, 2 or 3: x4

or x8;

**Environmental**

**Operating Temp:** 0° to 50° C **Storage Temp:** –20° to 90° C **Relative Humidity:** 0 to 95%, non-

cond. ••• Standard XA

**Size:** Standard XMC module, 2.91 in. x 5.87 in.

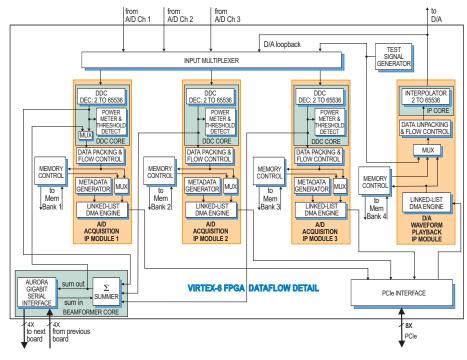

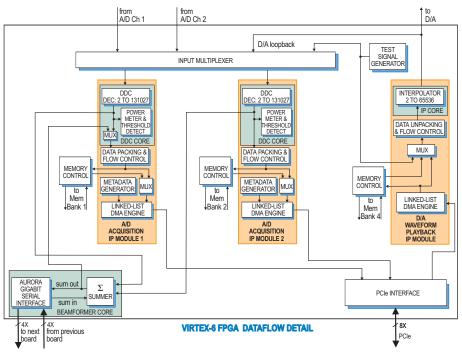

# Model 71621: Transceiver with Three A/Ds, DDCs, DUC, Two D/As - XMC

## **DDC IP Cores**

Within each A/D Acquisition IP Module is a powerful DDC IP core. Because of the flexible input routing of the A/D Acquisition IP Modules, many different configurations can be achieved including one A/D driving all three DDCs or each of the three A/Ds driving its own DDC.

Each DDC has an independent 32-bit tuning frequency setting that ranges from DC to  $f_s$ , where  $f_s$  is the A/D sampling frequency. Each DDC can have its own unique decimation setting, supporting as many as three different output bandwidths for the board. Decimations can be programmed from 2 to 65,536 providing a wide range to satisfy most applications.

The decimating filter for each DDC accepts a unique set of user-supplied 18-bit coefficients. The 80% default filters deliver an output bandwidth of  $0.8*f_s/N$ , where N is the decimation setting. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB. Each DDC delivers a complex output stream consisting of 24-bit I + 24-bit Q or16-bit I + 16-bit Q samples at a rate of  $f_s/N$ .

The model 71621 consists of a Model 71620 as described previously, but with the addition of three multiband DDCs, one interpolator and one beamformer

IP Cores installed in the Virtex-6 FPGA. These IP Cores are in addition to the factory-installed IP Modules described in the Model 71620.

## Interpolator IP Core

The DAC5688 provides interpolation factors of 2x, 4x and 8x. In addition to the DAC5688, an FPGA-based interpolator core provides additional interpolation from 2x to 65,536x.

The two interpolators can be combined to crate a total range from 2x to 524,288x.

### **Beamformer IP Core**

In addition to the DDCs, the 71621 features a complete beamforming subsystem. Each DDC core contains programable I & Q phase and gain adjustments followed by a power meter that continuously measures the individual average power output. The time constant of the averaging interval for each meter is programmable up to 8K samples. The power meters present average power measurements for each DDC core output in easy-to-read registers.

In addition, each DDC core includes a threshold detector to automatically send an interrupt to the processor if the average power level of any DDC core falls below or exceeds a programmable threshold.

A programmable summation block provides summing of any of the three DDC core outputs. An additional programmable gain stage compensates for summation change bit growth. A power meter and threshold detect block is provided for the summed output. The output is then directed back into the A/D Acquisition IP Module 1 FIFO for reading over the PCle. For larger systems, multiple 71621's can be chained together via a built-in Xilinx Aurora gigabit serial interface through the P16 XMC connector. This allows summation across channels on multiple boards.

# Model 71621: Transceiver with Three A/Ds, DDCs, DUC, Two D/As - XMC

## Also Available

| Model | Format                   |

|-------|--------------------------|

| 78621 | x8 PCI Express           |

| 53621 | 3U OpenVPX - Format 1    |

| 52621 | 3U OpenVPX - Format 2    |

| 56621 | AMC                      |

| 73621 | 3U cPCI - Single Density |

| 72621 | 6U cPCI - Single Density |

| 74621 | 6U cPCI - Double Density |

|       |                          |

### **Specifications**

### **Front Panel Analog Signal Inputs Input Type:** Transformer-coupled, front panel female SSMC connectors

Transformer Type: Coil Craft

WBC4-6TLB

Full Scale Input: +8 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

### A/D Converters

**Type:** Texas Instruments ADS5485 **Sampling Rate:** 10 MHz to 200 MHz

### **Resolution:** 16 bits **Digital Downconverters**

**Quantity:** Three channels

**Decimation Range:** 2x to 65,536x in

two stages of 2x to 256x

LO Tuning Freq. Resolution: 32 bits,

0 to  $f_s$

**LO SFDR:** >120 dB

Phase Offset Resolution: 32 bits,

0 to 360 degrees

FIR Filter: 18-bit coefficients, 24-bit output, with user programmable coef-

Default Filter Set: 80% bandwidth, <0.3 dB passband ripple, >100 dB stopband attenuation

### **D/A Converters**

**Type:** Texas Instruments DAC5688 **Input Data Rate:** 250 MHz max. Output IF: DC to 400 MHz max. Output Signal: 2-channel real or 1-channel with frequency translation **Output Sampling Rate:** 800 MHz max. with 2x, 4x or 8x interpolation

Resolution: 16 bits **Digital Interpolator**

**Interpolation Range:** 2x to 65,536x in two stages of 2x to 256x

### Beamformer

**Summation:** Three channels on-board; multiple boards can be summed via Summation Expansion Chain

Summation Expansion Chain: One chain in and one chain out link via XMC connector using Aurora protocol

**Phase Shift Coefficients:** | & Q with 16-bit resolution

Gain Coefficients: 16-bit resolution Channel Summation: 24-bit **Multiboard Summation Expansion:**

### **Front Panel Analog Signal Outputs**

Output: Transformer-coupled, front panel female SSMC connectors Transformer: Coil Craft WBC4-6TLB Full Scale Output: +4 dBm into 50 ohms

3 dB Passband: 300 kHz to 700 MHz **Sample Clock Sources:** On-board clock synthesizer generates two clocks:

one A/D clock and one D/A clock

### **Clock Synthesizer**

Clock Source: Selectable from onboard programmable VCXO (10 to 810 MHz), front panel external clock or LVPECL timing bus **Synchronization:** VCXO can be locked to an external 4 to 180 MHz PLL system reference, typically 10 MHz Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

### **External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 10 to 800 MHz divider input clock or PLL system reference

Timing Bus: 26-pin connector LVPECL bus includes, clock/sync/gate/PPS inputs and outputs; TTL signal for gate/trigger and sync/PPS inputs

## **Field Programmable Gate Array**

Standard: Xilinx Virtex-6 XC6VLX240T

**Optional:** Xilinx Virtex-6 XC6VSX315T

### Custom I/O

Option -104: Installs the PMC P14 connector with 20 LVDS pairs to the FPGA

### Memory

**Option 150 or 160:** Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR

**Option 155 or 165:** Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

### **PCI-Express Interface**

PCI Express Bus: Gen. 1: x4 or x8; Gen. 2: x4

### **Environmental**

Operating Temp: 0° to 50° C **Storage Temp:**  $-20^{\circ}$  to  $90^{\circ}$  C Relative Humidity: 0 to 95%, non-

Size: Standard XMC module, 2.91 in. x 5.87 in.

# Models 71630 & 71730: 1 GHz A/D, 1 GHz D/A - XMC

Model 71630 is a member of the **Cobalt** family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. Model 71730 is a member of the **Onyx** family of high-performance modules based on the Virtex-7 PGA.

These high-speed data converters are suitable for connection to HF or IF ports of a communications or radar system. Their built-in data capture and playback features offer an ideal turnkey solution.

Each model includes a 1 GHz A/D and a 1 GHz D/A converter and four banks of memory. In addition to supporting PCI Express as a native interface, these models include optional general purpose and gigabit serial connectors for application-specific I/O.

### **Features**

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT or Virtex-7 FPGAs

- Model 71730: GateXpress supports dynamic FPGA reconfiguration across PCle

- One 1 GHz 12-bit A/D

- One 1 GHz 16-bit D/A

- Model 71630: Up to 2 GB of DDR3 SDRAM or 32 MB of QDRII+ SRAM; Model 71730: 4 GB of DDR3 SDRAM

- Sample clock synchronization to an external system reference

- LVPECL sync bus for multimodule synchronization

- Dual-µSync clock/sync bus for multimodule synchronization

- Model 71630: PCI Express (Gen. 1 & 2) interface up to x8; Model 71730: PCI Express (Gen. 1, 2 and 3) interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

Contact Pentek for availability of rugged and conduction-cooled versions

### - A/D Converter

The front end accepts an analog HF or IF input on a front panel SSMC connector with transformer coupling into a Texas Instruments ADS5400 1 GHz, 12-bit A/D converter.

The digital outputs are delivered into the Virtex-6 or -7 FPGA for signal processing, data capture or for routing to other module resources.

## D/A Converter

Both models feature a TI DAC5681Z 1 GHz, 16-bit D/A. The converter has an input sample rate of 1 GSPS, allowing it to acept full rate data from the FPGA. Additionally, the D/A includes a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4 rate input data. Analog output is transformer-coupled to a front panel SSMC connector.

# Models 71630 & 71730: 1 GHz A/D, 1 GHz D/A - XMC

## Installed IP Modules

The factory-installed functions in both models include an A/D acquisition and a D/A waveform playback IP module.

In addition, IP modules for either

DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factoryinstalled functions and enable these models to operate as complete turnkey solutions, without the need to develop any FPGA IP.

## A/D Acquisition IP Module

Both models feature an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

# D/A Waveform Playback IP Module

The factory-installed functions in these models include a sophisticated D/A Waveform Playback IP module. A linked-list controller allows users to easily play back waveforms stored in either on-board memory or off- board host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

# Models 71630 & 71730: 1 GHz A/D, 1 GHz D/A - XMC

## Also Available

| Model | Format                   |

|-------|--------------------------|

| 78630 | x8 PCI Express           |

| 53630 | 3U OpenVPX - Format 1    |

| 52630 | 3U OpenVPX - Format 2    |

| 56630 | AMC                      |

| 73630 | 3U cPCI - Single Density |

| 72630 | 6U cPCI - Single Density |

| 74630 | 6U cPCI - Double Density |

|       |                          |

| Model | Format                   |

|-------|--------------------------|

| 78730 | x8 PCI Express           |

| 53730 | 3U OpenVPX - Format 1    |

| 52730 | 3U OpenVPX - Format 2    |

| 56730 | AMC                      |

| 73730 | 3U cPCI - Single Density |

| 72730 | 6U cPCI - Single Density |

| 74730 | 6U cPCI - Double Density |

|       |                          |

## Specifications -

## Front Panel Analog Signal Inputs

**Input Type:** Transformer-coupled, front panel female SSMC connectors

### A/D Converter

**Type:** Texas Instruments ADS5400 **Sampling Rate:** 100 MHz to 1 GHz **Resolution:** 12 bits

### D/A Converter

Type: Texas Instruments DAC5681Z Input Data Rate: 1 GHz max. Interpolation Filter: bypass, 2x or 4x Output Sampling Rate: 1 GHz max. Resolution: 16 bits

### **Front Panel Analog Signal Outputs**

**Output Type:** Transformer-coupled, front panel female SSMC connectors

# Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

### **Clock Synthesizer**

**Clock Source:** Selectable from onboard programmable VCXO or front panel external clock

**VCXO Frequency Ranges**: 10 to 945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phase-locked to an external 4 to 200 MHz PLL system reference, typically 10 MHz

**Clock Dividers**: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

### **External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

**Timing Bus:** 19-pin μSync bus connector, includes sync and gate/trigger inputs, CML

### **External Trigger Input**

**Type:** Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

### Model 71630 Xilinx Virtex-6 FPGA

**Standard:** CXC6VLX130T **Optional:** XC6VLX240T, or XC6VSX315T

### Model 71730 Xilinx Virtex-7 FPGA

Standard: XC7VX330T-2 Optional: XC7VX690T-2

### Custom I/O

**Option -104:** Installs the PMC P14 connector with 20 LVDS pairs (Model 71630) or 24 pairs (Model 71730) to the FPGA

**Option -105:** Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the FPGA

### Memory

Model 71630

**Option 150 or 160:** Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR

**Option 155 or 165:** Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

Model 71730

Type: DDR3 SDRAM

**Size:** Four banks, 1 GB each, 800 MHz (1600 MHz DDR)

## **PCI-Express Interface**

Model 71630

**PCI Express Bus:** Gen. 1: x4 or x8; Gen. 2: x4

Model 71730

**PCI Express Bus:** Gen. 1, 2 or 3: x4 or x8

### **Environmental**

**Operating Temp:** 0° to 50° C **Storage Temp:** –20° to 90° C **Relative Humidity:** 0 to 95%, noncond.

**Size:** Standard XMC module, 2.91 in. x 5.87 in.

# Model 71640: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D - XMC

Model 71640 is a member of the Cobalt family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. A high-speed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture features offer an ideal turnkey solution as well as a plat-

form for developing and deploying custom FPGA processing IP.

It includes a 3.6 GHz, 12-bit A/D converter and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71640 includes optional general purpose and gigabit serial connectors for application-specific I/O.

### A/D Converter

The front end accepts analog HF or IF inputs on a pair of front panel SSMC connectors with transformer coupling into a Texas Instruments ADC12D1800 12-bit A/D. The converter operates in single-channel interleaved mode with a sampling rate of 3.6 GHz and an input bandwidth of 1.75 GHz; or, in dual-channel mode with a sampling rate of 1.8 GHz and input bandwidth of 2.8 GHz.

The ADC12D1800 provides a programmable 15-bit gain adjustment allowing the 71640 to have a full scale input range of +2 dBm to +4 dBm. A built-in AutoSync feature supports A/D synchronization across multiple modules.

The A/D digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

### **Features**

- Ideal radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- One-channel mode with 3.6 GHz, 12-bit A/D

- Two-channel mode with 1.8 GHz, 12-bit A/Ds

- 2 GB of DDR3 SDRAM

- Sync bus for multimodule synchronization

- PCI Express Gen. 2 interface x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

Contact Pentek for availability of rugged and conduction-cooled versions

# Model 71640: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D - XMC

## **Installed IP Modules**

The 71640 factory-installed functions include an A/D acquisition IP module. In addition, IP modules for DDR3 memories, a controller for all data

clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 71640 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

## A/D Acquisition IP Module

The 71640 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, or a test signal generator. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. In single-channel mode, all four banks are used to store the single-channel of input data. In dual-channel mode, memory banks 1 and 2 store data from input channel 1 and memory banks 3 and 4 store data from input channel 2. In both modes, continuous, full-rate transient capture of 12-bit data is supported.

The memory banks are supported with a DMA engine for moving A/D

data through the PCIe interface. This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

# Model 71640: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D - XMC

## Also Available

| Model | Format                   |

|-------|--------------------------|

| 78640 | x8 PCI Express           |

| 53640 | 3U OpenVPX - Format 1    |

| 52640 | 3U OpenVPX - Format 2    |

| 56640 | AMC                      |

| 73640 | 3U cPCI - Single Density |

| 72640 | 6U cPCI - Single Density |

| 74640 | 6U cPCI - Double Density |

|       |                          |

## **Specifications**

## **Front Panel Analog Signal Inputs** Input Type: Transformer-coupled,

front panel female SSMC connectors

### A/D Converter

**Type:** Texas Instruments ADC12D1800

**Sampling Rate:** Single-channel mode: 500 MHz to 3.6 GHz; dual-channel mode: 150 MHz to 1.8 GHz

**Resolution:** 12 bits

**Input Bandwidth:** single-channel mode: 1.75 GHz; dual-channel

mode: 2.8 GHz

Full Scale Input: +2 dBm to +4 dBm, programmable

Sample Clock Sources: Front panel

SSMC connector Sync Bus: Multi-pin connectors, bus includes gate, reset and in and out ref clock

**External Trigger Input**

**Type:** Front panel female SSMC

connector, TTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

**Field Programmable Gate Array**

Standard: Xilinx Virtex-6

XC6VLX130T-2

**Optional:** Xilinx Virtex-6

XC6VLX240T-2 or XC6VSX315T-2

### Custom I/O

Option -104: Installs the PMC P14 connector with 20 LVDS pairs to the FPGA

Option -105: Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the **FPGA**

Memory: Four 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

**PCI-Express Interface**

PCI Express Bus: Gen. 1 or Gen. 2: x4 or x8

**Environmental**

Operating Temp:  $0^{\circ}$  to  $50^{\circ}$  C **Storage Temp:**  $-20^{\circ}$  to  $90^{\circ}$  C Relative Humidity: 0 to 95%, non-

Size: Standard XMC module, 2.91 in. x 5.87 in.

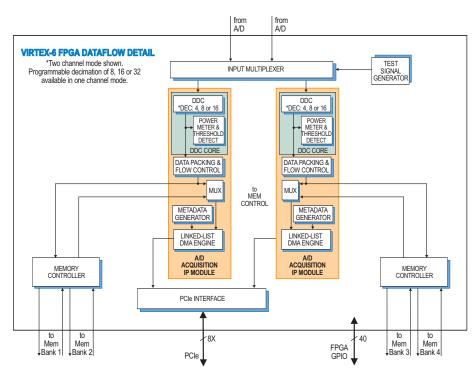

# Model 71641: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, w/ DDC- XMC

The model 71641 consists of a Model 71640 as described previously, but with the addition of two wideband DDC IP Cores installed in the Virtex-6 FPGA.

These IP Cores are in addition to the factory-installed IP Modules described in the Model 71640.

### **DDC IP Cores**

Within the FPGA is a powerful DDC IP core. The core supports a single-channel mode, accepting data samples from the A/D at the full 3.6 GHz rate. Additionally, a dual-channel mode supports the A/D's 1.8 GHz two-channel operation .

In dual-channel mode, each DDC has an independent 32-bit tuning frequency setting that ranges from DC to  $f_s$ , where  $f_s$  is the A/D sampling frequency.

In single-channel mode, decimation can be programmed to 8x, 16x

or 32x. In dual-channel mode, both channels share the same decimation rate, programmable to 4x, 8x or 16x.

The decimating filter for each DDC accepts a unique set of user-supplied 16-bit coefficients. The 80% default filters deliver an output bandwidth of  $0.8*f_s/N$ , where N is the decimation setting. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB. Each DDC delivers a complex output stream consisting of 16-bit I + 16-bit Q samples at a rate of  $f_s/N$ .

# Model 71641: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, w/ DDC- XMC

## Also Available -

| Model | Format                   |

|-------|--------------------------|

| 78641 | x8 PCI Express           |

| 53641 | 3U OpenVPX - Format 1    |

| 52641 | 3U OpenVPX - Format 2    |

| 56641 | AMC                      |

| 73641 | 3U cPCI - Single Density |

| 72641 | 6U cPCI - Single Density |

| 74641 | 6U cPCI - Double Density |

|       |                          |

## **Specifications** .

### **Front Panel Analog Signal Inputs**

**Input Type:** Transformer-coupled, front panel female SSMC connectors

### A/D Converter

**Type:** Texas Instruments ADC12D1800

Sampling Rate: Single-channel mode: 500 MHz to 3.6 GHz; dualchannel mode: 150 MHz to 1.8 GHz

**Resolution:** 12 bits

**Input Bandwidth:** single-channel mode: 1.75 GHz; dual-channel

mode: 2.8 GHz

Full Scale Input: +2 dBm to +4 dBm, programmable

### **Digital Downconverters**

**Modes:** One or two channels, programmable

Supported Sample Rate: One-channel mode: 3.6 GHz, two-channel mode: 1.8 GHz

**Decimation Range:** One-channel mode: 8x, 16x or 32x, two-channel mode: 4x, 8x, or 16x

LO Tuning Freq. Resolution: 32 bits, 0 to  $f_c$

**LO SFDR:** >120 dB

Phase Offset Resolution: 32 bits,

0 to 360 degrees

FIR Filter: User-programmable 18-bit

coefficients

Default Filter Set: 80% bandwidth, <0.3 dB passband ripple, >100 dB stopband attenuation

Sample Clock Sources: Front panel

SSMC connector

Sync Bus: Multipin front panel connector, includes gate, reset, and in and out ref clock

### **External Trigger Input**

**Type:** Front panel female SSMC connector, TTL

Function: Programmable functions include trigger and gate

### **Field Programmable Gate Array:** Xilinx Virtex-6 XC6VSX315T-2

### Custom I/O

Option -104: Installs the PMC P14 connector with 20 LVDS pairs to the FPGA

**Memory:** Four 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

### **PCI-Express Interface**

PCI Express Bus: Gen. 1 or Gen. 2: x4 or x8

### **Environmental**

Operating Temp:  $0^{\circ}$  to  $50^{\circ}$  C Storage Temp: -20° to 90° C Relative Humidity: 0 to 95%, non-

Size: Standard XMC module, 2.91 in. x 5.87 in.

# Model 71741: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, w/ DDC - XMC

Model 71741 is a member of the Onyx® family of high-performance XMC modules based on the Xilinx Virtex-7 FPGA. A high-speed data converter with a programmable digital downconverter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture features offer an ideal turnkey solution.

It includes a 3.6 GHz, 12-bit A/D converter and four banks of memory. In addition to supporting PCI Express Gen. 3 as a native interface, Model 71741 includes an optional connection to the Virtex-7 FPGA for custom I/O.

The model 71741 includes two wideband DDC IP cores factory-installed in the Virtex-7 FPGA.

### A/D Converter

The front end accepts analog HF or IF inputs on a pair of front panel SSMC connectors with transformer-coupling into a Texas Instruments ADC12D1800 12-bit A/D. The converter operates in single-channel interleaved mode with a sampling rate of 3.6 GHz and an input bandwidth of 1.75 GHz; or, in dual-channel mode with a sampling rate of 1.8 GHz and input bandwidth of 2.8 GHz.

The ADC12D1800 provides a programmable 15-bit gain adjustment allowing the 71741 to have a full scale input range of +2 dBm to +4 dBm. A built-in AutoSync feature supports A/D synchronization across multiple modules.

The A/D digital outputs are delivered into the Virtex-7 FPGA for signal processing, data capture or for routing to other module resources.

### **Features**

- Ideal radar and software radio interface solution

- Supports Xilinx Virtex-7 VXT FPGAs

- GateXpress supports dynamic FPGA reconfiguration across PCIe

- One-channel mode with 3.6 GHz, 12-bit A/D

- Two-channel mode with 1.8 GHz, 12-bit A/Ds

- Programmable one- or two- channel DDC (Digital Downconverter)

- 4 GB of DDR3 SDRAM

- µSync clock/sync bus for multimodule synchronization

- PCI Express (Gen. 1, 2 & 3) interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-7 FPGA for custom I/O

Contact Pentek for availability of rugged and conduction-cooled versions

# Model 71741: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, w/ DDC - XMC

## **Installed IP Modules**

The 71741 factory-installed functions include an A/D acquisition IP module and a programmable DDC (digital downconverter). In addition, IP mod-

ules for DDR3 SDRAM memories, a controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 71741 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

## A/D Acquisition IP Module

The 71741 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, or a test signal generator. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. In single-channel mode, all four banks are used to store the single-channel of input data. In dual-channel mode, memory banks 1 and 2 store data from input channel 1 and memory banks 3 and 4 store data from input channel 2. In both modes, continuous, full-rate transient capture of 12-bit data is supported.

The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface. This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp and data length information. These actions simplify the host processor's job of identifying and executing on the data.

## **DDC IP Cores**

Within the FPGA is a powerful DDC IP core. The core supports a single-channel mode, accepting data samples from the A/D at the full 3.6 GHz rate. Additionally, a dual-channel mode supports the A/D's 1.8 GHz two-channel operation .

In dual-channel mode, each DDC has an independent 32-bit tuning frequency setting that ranges from DC to  $f_s$ , where  $f_s$  is the A/D sampling frequency.

In single-channel mode, decimation can be programmed to 8x, 16x

or 32x. In dual-channel mode, both channels share the same decimation rate, programmable to 4x, 8x or 16x.

The decimating filter for each DDC accepts a unique set of user-supplied 16-bit coefficients. The 80% default filters deliver an output bandwidth of  $0.8*f_s/N$ , where N is the decimation setting. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB. Each DDC delivers a complex output stream consisting of 16-bit I + 16-bit Q samples at a rate of  $f_s/N$ .

# Model 71741: 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, w/ DDC - XMC

### Also Available

| Model | Format                   |

|-------|--------------------------|

| 78741 | x8 PCI Express           |

| 53741 | 3U OpenVPX - Format 1    |

| 52741 | 3U OpenVPX - Format 2    |

| 56741 | AMC                      |

| 73741 | 3U cPCI - Single Density |

| 72741 | 6U cPCI - Single Density |

| 74741 | 6U cPCI - Double Density |

### **Specifications**

**Front Panel Analog Signal Inputs** Input Type: Transformer-coupled, front panel female SSMC connectors

A/D Converter

**Type:** Texas Instruments

ADC12D1800

Sampling Rate: Single-channel mode: 500 MHz to 3.6 GHz; dualchannel mode: 150 MHz to 1.8 GHz

**Resolution:** 12 bits

Input Bandwidth: single-channel mode: 1.75 GHz; dual-channel

mode: 2.8 GHz

Full Scale Input: +2 dBm to +4 dBm, programmable

**Digital Downconverters**

Modes: One or two channels,

programmable

Supported Sample Rate: One-channel mode: 3.6 GHz, two-channel

mode: 1.8 GHz

**Decimation Range:** One-channel mode: 8x, 16x or 32x, two-channel mode: 4x, 8x, or 16x

LO Tuning Freq. Resolution: 32 bits,

0 to  $f_s$

**LO SFDR:** >120 dB

Phase Offset Resolution: 32 bits,

0 to 360 degrees

FIR Filter: User-programmable 18-bit

coefficients

Default Filter Set: 80% bandwidth, <0.3 dB passband ripple, >100 dB

stopband attenuation

Sample Clock Source: Front panel

SSMC connector

Timing Bus: 19-pin µSync bus connector includes sync and gate/trigger inputs, CML

**External Trigger Input**

**Type:** Front panel female SSMC

connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

**Field Programmable Gate Array**

Standard: Xilinx Virtex-7

XC7VX330T-2

**Optional:** Xilinx Virtex-7

XC7VX690T-2

Custom I/O

Option -104: Installs the PMC P14 connector with 24 LVDS pairs to

the FPGA

Option -105: Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the

**FPGA**

Memory Type: DDR3 SDRAM

Size: Four banks, 1 GB each

**Speed:** 800 MHz (1600 MHz DDR)

**PCI-Express Interface**

PCI Express Bus: Gen. 1, 2 or 3: x4

or x8

**Environmental**

Operating Temp: 0° to 50° C Storage Temp:  $-20^{\circ}$  to  $90^{\circ}$  C Relative Humidity: 0 to 95%, non-

Size: Standard XMC module, 2.91 in. x

5.87 in.

# Model 71650: Transceiver with Two A/Ds, DUC, Two D/As - XMC

Model 71650 is a member of the Cobalt family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. A multichannel, high-speed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture and playback features offer an ideal turnkey solution as well as a platform

for developing and deploying custom FPGA processing IP.

It includes two A/Ds, one DUC, two D/As, and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71650 includes optional general-purpose and gigabit serial card connectors for application-specific I/O.

## A/D Converter

The front end accepts two full-scale analog HF or IF inputs on front panel SSMC connectors at +5 dBm into 50 ohms with transformer coupling into two Texas Instruments ADS5463 500 MHz, 12-bit A/D converters.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

## Digital Upconverter and D/As

A TI DAC5688 DUC and D/A accepts a baseband real or complex data stream from the FPGA which is optionally interpolated, upconverted and then delivered to the two D/As.