#### MODEL

#### **DESCRIPTION**

| <u>Cobalt 71630</u>               | 1 GHz A/D and D/A, Virtex-6 FPGA - XMC                                     |

|-----------------------------------|----------------------------------------------------------------------------|

| <u>Cobalt 78630</u>               | 1 GHz A/D and D/A, Virtex-6 FPGA - x8 PCIe                                 |

| <u>Cobalt 53630</u>               | 1 GHz A/D and D/A, Virtex-6 FPGA - 3U VPX - Format 1                       |

| <u>Cobalt 52630</u>               | 1 GHz A/D and D/A, Virtex-6 FPGA - 3U VPX - Format 2                       |

| Cobalt 57630 & 58630              | 1-/2-Ch 1 GHz A/D and 1-/2-Ch 1 GHz D/A, Virtex-6 FPGA - 6U VPX            |

| Cobalt 72630, 73630, 74630        | 1-/2-Ch 1 GHz A/D and 1-/2-Ch 1 GHz D/A, Virtex-6 FPGA - 6U/3U cPCI        |

| <u>Cobalt 56630</u>               | 1 GHz A/D and D/A, Virtex-6 FPGA - AMC                                     |

| <u>Cobalt 71640</u>               | 1-Ch 3.6 GHz or 2-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - XMC               |

| <u>Cobalt 78640</u>               | 1-Ch 3.6 GHz or 2-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - x8 PCIe           |

| <u>Cobalt 53640</u>               | 1-Ch 3.6 GHz or 2-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - 3U VPX - Format 1 |

| Cobalt 52640                      | 1-Ch 3.6 GHz or 2-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - 3U VPX - Format 2 |

| Cobalt 57640 & 58640              | 1-/2-Ch 3.6 GHz or 2-/4-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - 6U VPX      |

| Cobalt 72640, 73640, 74640        | 1-/2-Ch 3.6 GHz or 2-/4-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - 6U/3U cPCI  |

| <u>Cobalt 56640</u>               | 1-Ch 3.6 GHz or 2-Ch 1.8 GHz 12-bit A/D, Virtex-6 FPGA - AMC               |

| <u>Cobalt 71660</u>               | 4-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - XMC                         |

| <u>Cobalt 78660</u>               | 4-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - x8 PCIe                     |

| <u>Cobalt 53660</u>               | 4-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - 3U VPX - Format 1           |

| <u>Cobalt 52660</u>               | 4-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - 3U VPX - Format 2           |

| <u>Cobalt 57660 &amp; 58660</u>   | 4-/8-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - 6U VPX                   |

| <u>Cobalt 72660, 73660, 74660</u> | 4-/8-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - 6U/3U cPCI               |

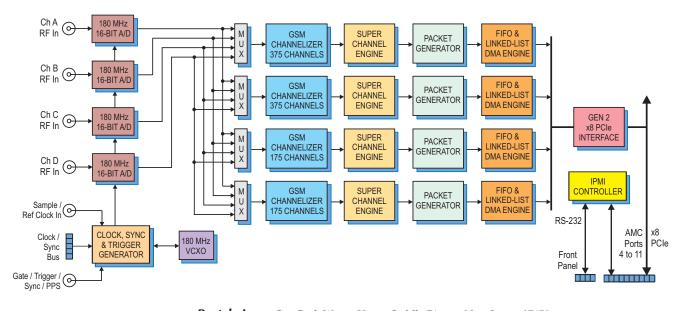

| <u>Cobalt 56660</u>               | 4-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - AMC                         |

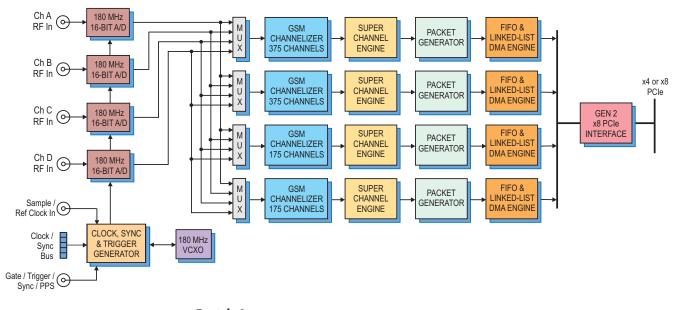

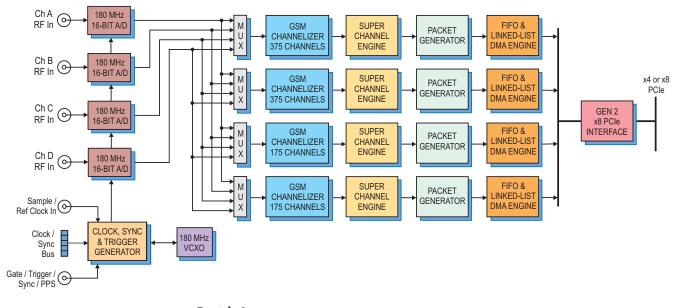

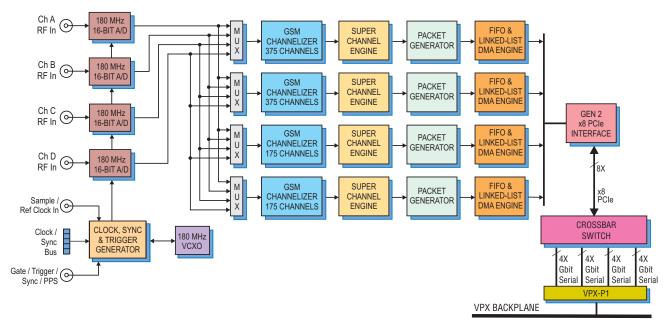

| <u>Cobalt 71663</u>               | 1100 GSM Channelizer with Quad A/D - XMC                                   |

| <u>Cobalt 78663</u>               | 1100 GSM Channelizer with Quad A/D - x8 PCIe                               |

| <u>Cobalt 53663</u>               | 1100 GSM Channelizer with Quad A/D - 3U VPX - Format 1                     |

| <u>Cobalt 52663</u>               | 1100 GSM Channelizer with Quad A/D - 3U VPX - Format 2                     |

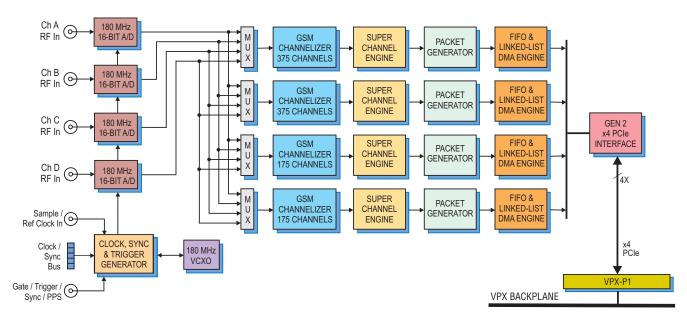

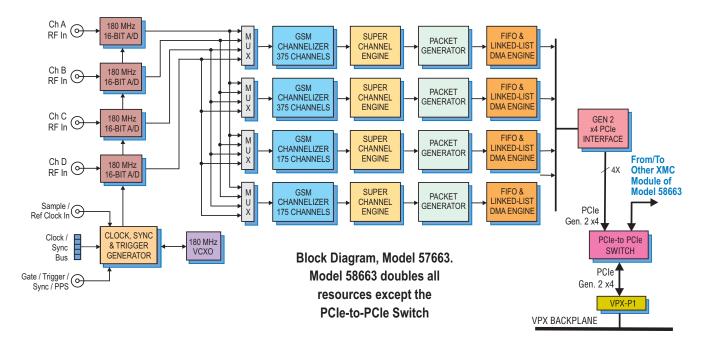

| Cobalt 57663 & 58663              | 1100/2200 GSM Channelizer with Quad/Octal A/D - 6U VPX                     |

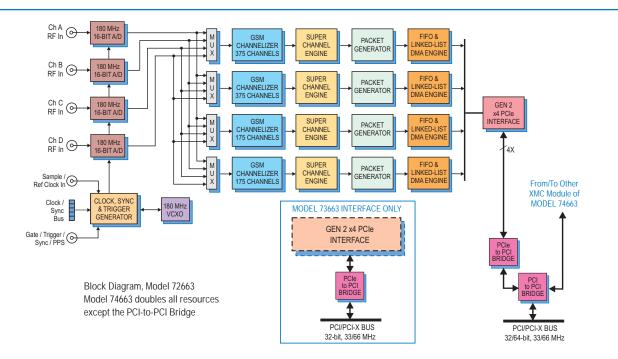

| Cobalt 72663, 73663, 74663        | 1100/2200 GSM Channelizer with Quad/Octal A/D - 6U/3U cPCI                 |

| <u>Cobalt 56663</u>               | 1100 GSM Channelizer with Quad A/D - AMC                                   |

| <u>Cobalt 71670</u>               | 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - XMC                       |

| <u>Cobalt 78670</u>               | 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - x8 PCIe                   |

| <u>Cobalt 53670</u>               | 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - 3U VPX - Format 1         |

| <u>Cobalt 52670</u>               | 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - 3U VPX - Format 2         |

| Cobalt 57670 & 58670              | 4-/8-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - 6U VPX                 |

| Cobalt 72670, 73670, 74670        | 4-/8-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - 6U/3U cPCI             |

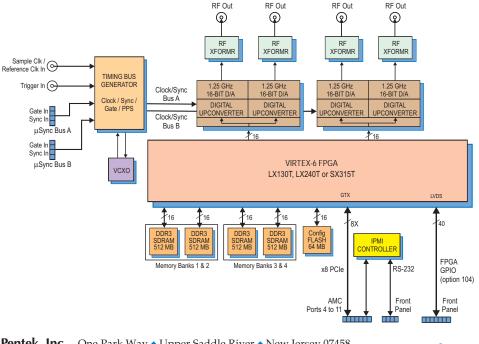

| <u>Cobalt 56670</u>               | 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - AMC                       |

| <u>Cobalt 71690</u>               | L-Band RF Tuner, 2-Channel 200 MHz A/D, Virtex-6 FPGA - XMC                |

| <u>Cobalt 78690</u>               | L-Band RF Tuner, 2-Channel 200 MHz A/D, Virtex-6 FPGA - x8 PCIe            |

| <u>Cobalt 53690</u>               | L-Band RF Tuner, 2-Channel 200 MHz A/D, Virtex-6 FPGA - 3U VPX - Format 1  |

| <u>Cobalt 52690</u>               | L-Band RF Tuner, 2-Channel 200 MHz A/D, Virtex-6 FPGA - 3U VPX - Format 2  |

|                                   |                                                                            |

Click Here for the PRODUCT SELECTOR

Last updated: April 2018 <u>More on next page</u> www.pentek.com

#### MODEL

#### DESCRIPTION

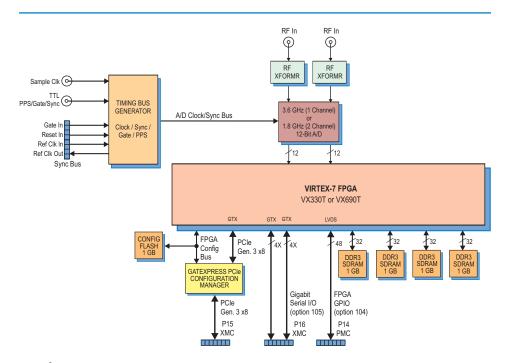

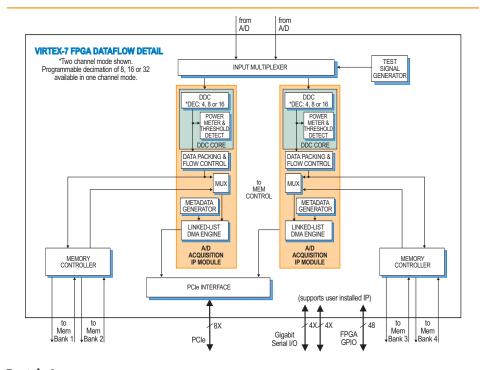

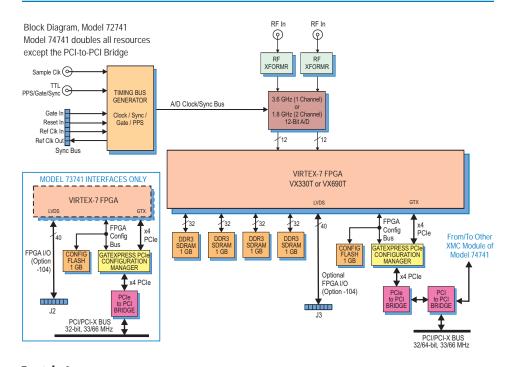

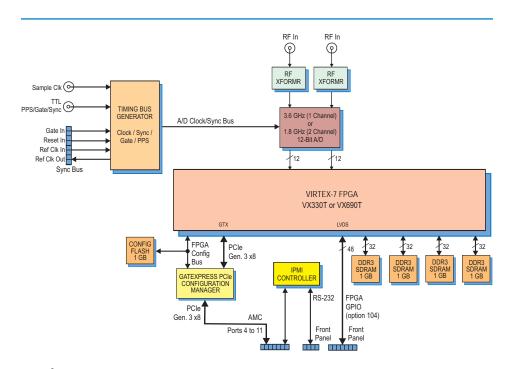

Cobalt 57690 & 58690 1-/2-Ch L-Band RF Tuner, 2-/4-Ch 200 MHz A/D, Virtex-6 FPGA - 6U VPX 1-/2-Ch L-Band RF Tuner, 2-/4-Ch 200 MHz A/D, Virtex-6 FPGA - 6U/3U cPCI Cobalt 72690, 73690, 74690 L-Band RF Tuner, 2-Channel 200 MHz A/D, Virtex-6 FPGA - AMC Cobalt 56690 <u>Onyx 71760</u> 4-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - XMC <u>Onyx 78760</u> 4-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - x8 PCIe 4-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - 3U VPX - Format 1 <u>Onyx 53760</u> 4-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - 3U VPX - Format 2 Onyx 52760 4-/8-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - 6U VPX Onyx 57760 & 58760 <u>Onyx 72760, 73760, 74760</u> 4-/8-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - 6U/3U cPCI Onyx 56760 4-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - AMC Onyx 71730 1 GHz A/D and D/A, Virtex-7 FPGA - XMC 1 GHz A/D and D/A, Virtex-7 FPGA - x8 PCIe <u>Onyx 78730</u> 1 GHz A/D and D/A, Virtex-7 FPGA - 3U VPX - Format 1 <u>Onyx 53730</u> 1 GHz A/D and D/A, Virtex-7 FPGA - 3U VPX - Format 2 Onyx 52730 1-/2-Ch 1 GHz A/D and 1-/2-Ch 1 GHz D/A, Virtex-7 FPGAs - 6U VPX <u>Onyx 57730 & 58730</u> 1-/2-Ch 1 GHz A/D and 1-/2-Ch 1 GHz D/A, Virtex-7 FPGAs - 6U/3U cPCI <u>Onyx 72730, 73730, 74730</u> 1 GHz A/D and D/A, Virtex-7 FPGA - AMC <u>Onyx 56730</u> <u>Onyx 71741</u> 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - XMC 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - x8 PCIe <u>Onyx 78741</u> 1-Ch. 3.6 GHz or 2-Ch. 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - 3U VPX - Format 1 <u>Onyx 53741</u> 1-Ch. 3.6 GHz or 2-Ch. 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - 3U VPX - Format 2 Onyx 52741 1/2-Ch. 3.6 GHz or 2/4-Ch. 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - 6U VPX Onyx 57741 & 58741 1/2-Ch. 3.6 GHz or 2/4-Ch. 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - 6U/3U cPCI <u>Onyx 72741, 73741, 74741</u> 1-Channel 3.6 GHz or 2-Channel 1.8 GHz, 12-bit A/D, DDC, Virtex-7 FPGA - AMC <u>Onyx 56741</u> Cobalt 71610 LVDS Digital I/O with Virtex-6 FPGA - XMC LVDS Digital I/O with Virtex-6 FPGA - x8 PCIe Cobalt 78610 Cobalt 53610 LVDS Digital I/O with Virtex-6 FPGA - 3U VPX - Format 1 Cobalt 52610 LVDS Digital I/O with Virtex-6 FPGA - 3U VPX - Format 2 Single or Dual LVDS Digital I/O with Virtex-6 FPGAs - 6U VPX Cobalt 57610 & 58610 Cobalt 72610, 73610, 74610 Single or Dual LVDS Digital I/O with Virtex-6 FPGAs - 6U/3U cPCI LVDS Digital I/O with Virtex-6 FPGA - AMC Cobalt 56610 Cobalt 7811 Quad Serial FPDP Interface with Virtex-6 FPGA - x8 PCIe Quad Serial FPDP Interface with Virtex-6 FPGA - XMC Cobalt 71611 Ouad Serial FPDP Interface with Virtex-6 FPGA - x8 PCIe Cobalt 78611 Quad Serial FPDP Interface with Virtex-6 FPGA - 3U VPX - Format 1 Cobalt 53611 Cobalt 52611 Quad Serial FPDP Interface with Virtex-6 FPGA - 3U VPX - Format 2 Quad or Octal Serial FPDP Interface with Virtex-6 FPGAs - 6U VPX Cobalt 57611 & 58611 Cobalt 72611, 73611, 74611 Quad or Octal Serial FPDP Interface with Virtex-6 FPGAs - 6U/3U cPCI Quad Serial FPDP Interface with Virtex-6 FPGA - AMC Cobalt 56611

Click Here for the PRODUCT SELECTOR

Last updated: April 2017 <u>More on next page</u> www.pentek.com

#### MODEL

#### **DESCRIPTION**

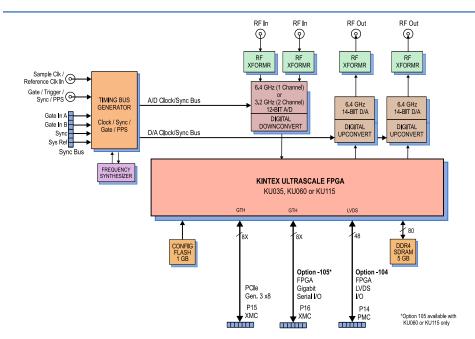

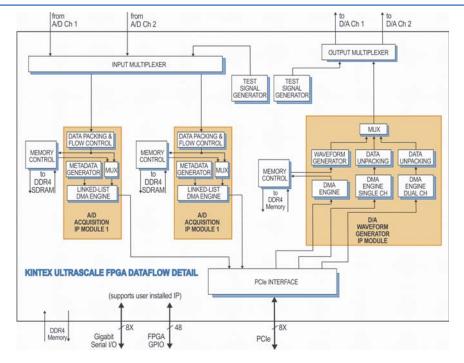

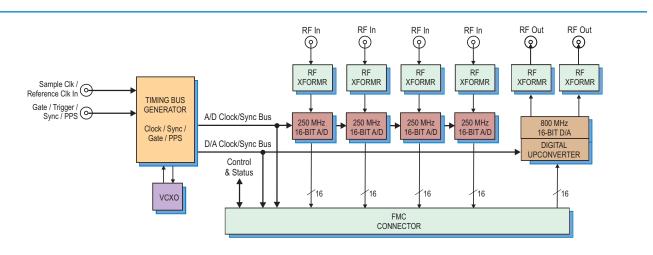

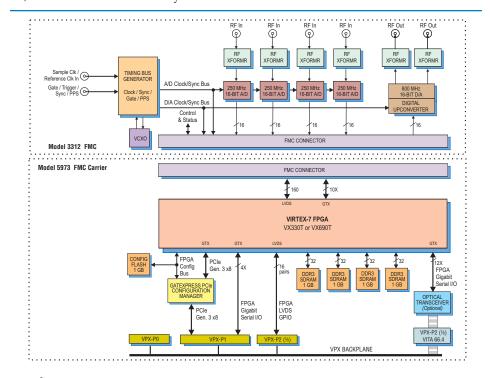

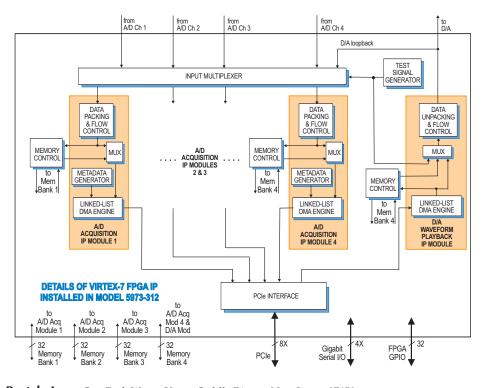

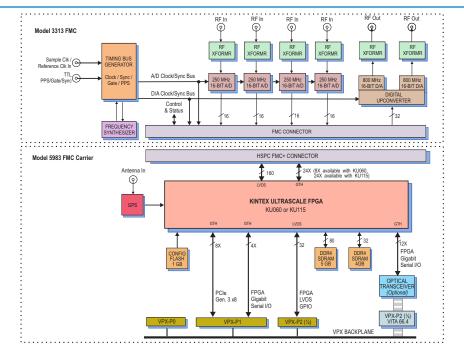

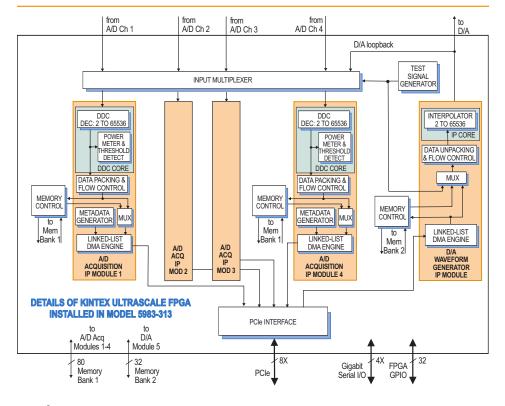

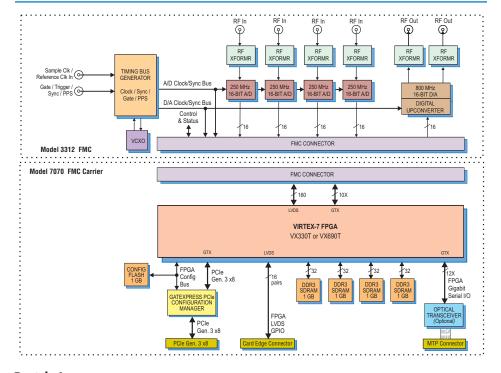

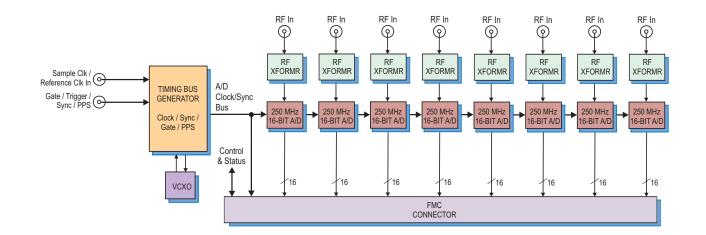

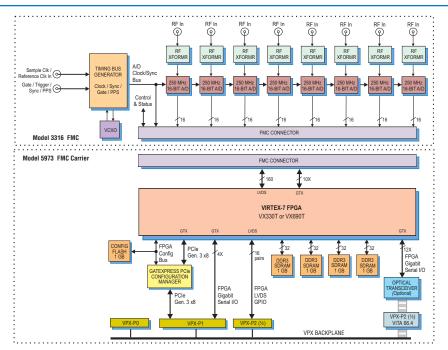

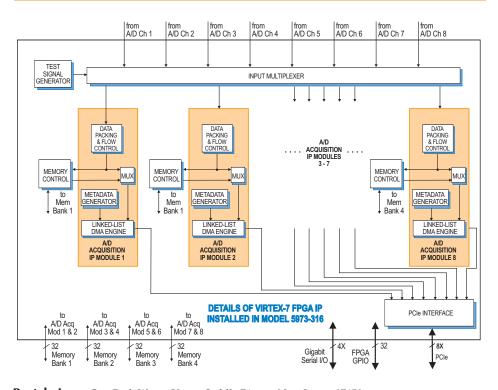

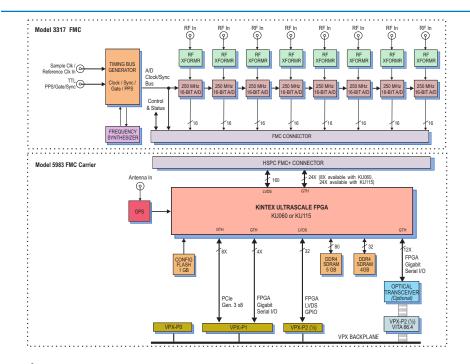

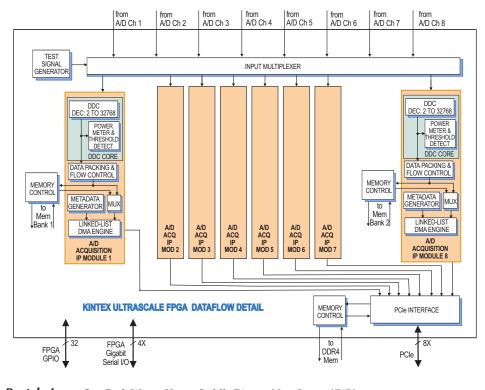

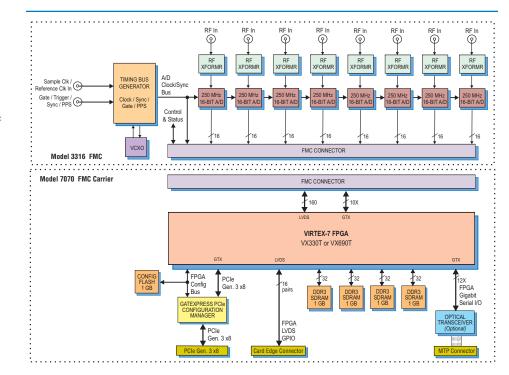

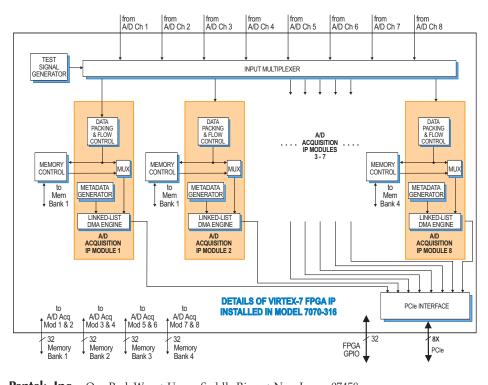

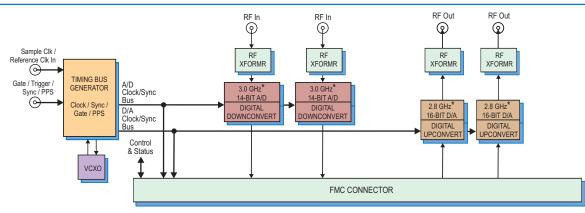

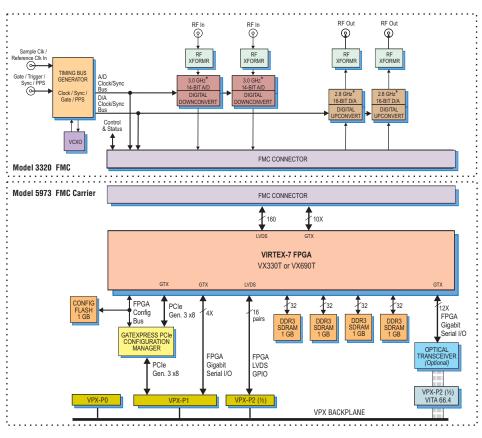

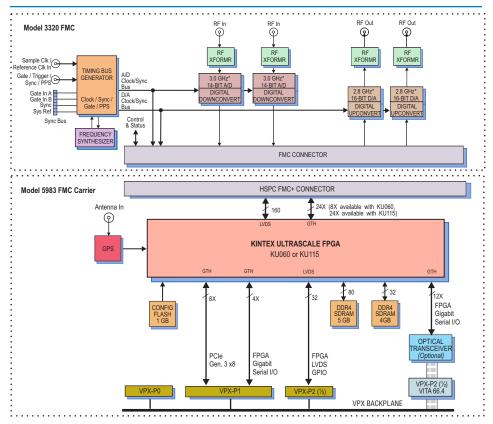

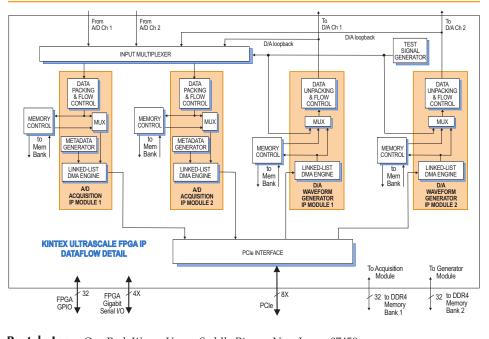

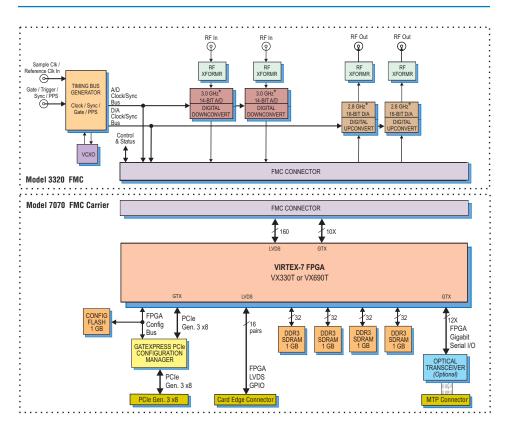

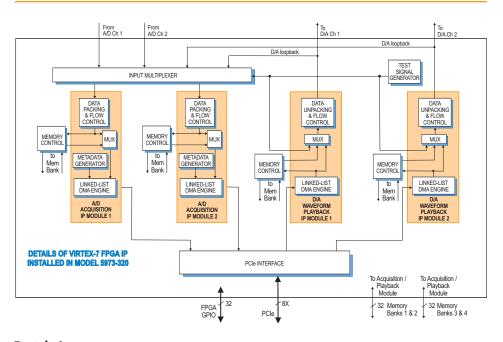

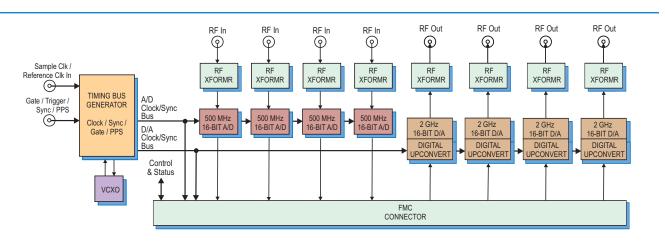

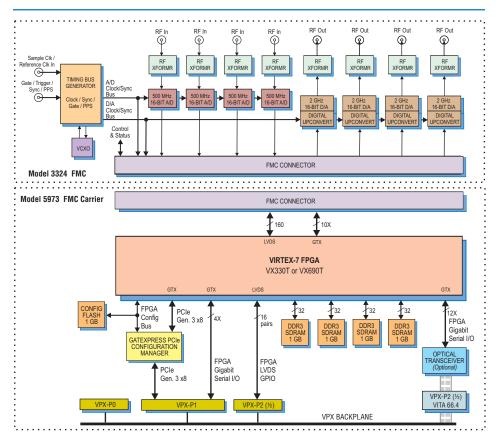

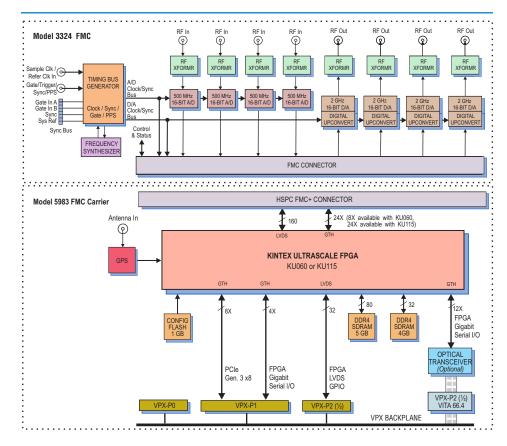

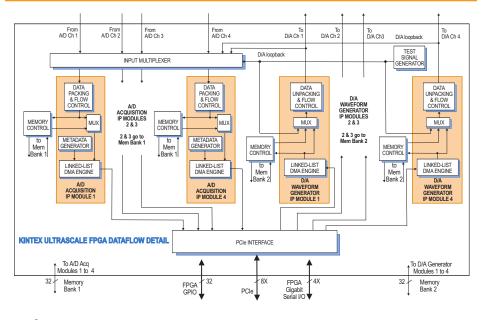

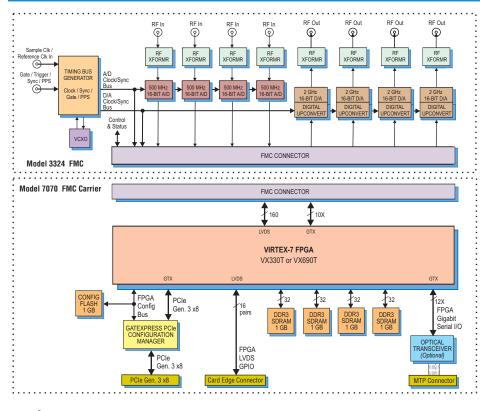

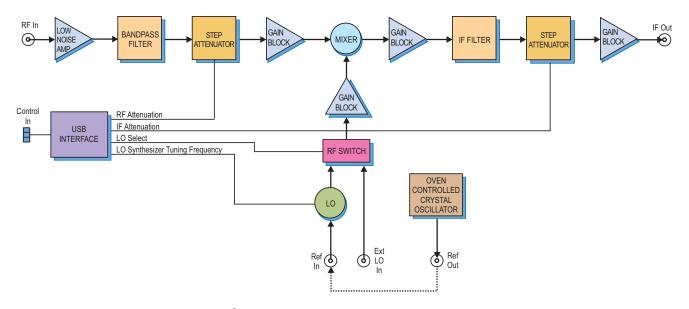

1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - XMC Jade 71141 Jade 78141 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - x8 PCIe Jade 53141 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - 3U VPX 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - 3U VPX Jade 52141 Jade 57141 & 58141 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - 6U VPX Jade 72141, 73141, 74141 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - 6U/3U cPCI Jade 56141 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, Kintex FPGA - AMC Flexor 5973 Virtex-7 Processor and FMC Carrier - 3U VPX Flexor 5983 Kintex UltraScale Processor and FMC Carrier - 3U VPX Flexor 7070 Virtex-7 Processor and FMC Carrier - x8 PCIe Flexor 3312 4-Channel 250 MHz, 16-bit A/D, 2-Channel 800 MHz, 16-bit D/A - FMC FlexorSet 5973-312 4-Channel 250 MHz 16-bit A/D, 2-Channel800 MHz 16-bit D/A - 3U VPX Kintex 4-Channel 250 MHz 16-bit A/D, 2-Channel 800 MHz 16-bit D/A - 3U VPX FlexorSet 5983-313 FlexorSet 7070-312 4-Channel 250 MHz 16-bit A/D, 2-Channel800 MHz 16-bit D/A - x8 PCIe 8-Channel 250 MHz, 16-bit A/D - FMC Flexor 3316 FlexorSet 5973-316 8-Channel 250 MHz 16-bit A/D with Virtex-7 FPGA - 3U VPX FlexorSet 5983-317 Kintex 4-Channel 250 MHz 16-bit A/D, with DDCs, 2-Channel 800 MHz 16-bit D/A - 3U VPX FlexorSet 7070-316 8-Channel 250 MHz 16-bit A/D with Virtex-7 FPGA - x8 PCIe 2-Channel 3.0 GHz A/D, 2-Channel 2.8 GHz D/A wth Virtex-7 - FMC Flexor 3320 FlexorSet 5973-320 2-Channel 3.0 GHz A/D, 2-Channel 2.8 GHz D/A wth Virtex-7 - 3U VPX FLexorSet 5983-320 Kintex 4-Channel 250 MHz 16-bit A/D, 2-Channel 800 MHz 16-bit D/A - 3U VPX FlexorSet 7070-320 2-Channel 3.0 GHz A/D, 2-Channel 2.8 GHz D/A wth Virtex-7 - x8 PCIe Flexor 3324 4-Channel 500 MHz, 16-bit A/D, 4-Channel 1.5 GHz, 16-bit D/A - FMC FlexorSet 5973-324 4-Channel 500 MHz, 16-bit A/D, 4-Channel 1.5 GHz, 16-bit D/A - 3U VPX FlexorSet 5983-324 Kintex 4-Channel 250 MHz 16-bit A/D, 2-Channel 800 MHz 16-bit D/A - 3U VPX FlexorSet 7070-324 4-Channel 500 MHz, 16-bit A/D, 4-Channel 1.5 GHz, 16-bit D/A - x8 PCIe Bandit 7120 Two-Channel Analog RF Wideband Downconverter - PMC/XMC Bandit 7820 Two-Channel Analog RF Wideband Downconverter - PCIe Bandit 5220 Two-Channel Analog RF Wideband Downconverter - 3U VPX Bandit 5720 & 5820 Two- or Four-Channel Analog RF Wideband Downconverter - 6U OpenVPX Bandit 7220, 7320, 7420 Two- or Four-Channel Analog RF Wideband Downconverter - 6U/3U cPCI Bandit 5620 Two-Channel Analog RF Wideband Downconverter - AMC Bandit 8111 Modular Analog RF Slot Downconverter Series 8264 6U OpenVPX Development System for Cobalt and Onyx Boards 8266 PC Development System for PCIe Cobalt and Onyx Boards 8267 3U VPX Development System for Cobalt, Onyx and Flexor Boards **Customer Information**

Click Here for the PRODUCT SELECTOR

#### Last updated: April 2018

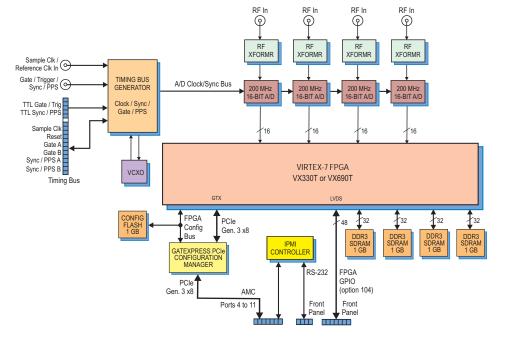

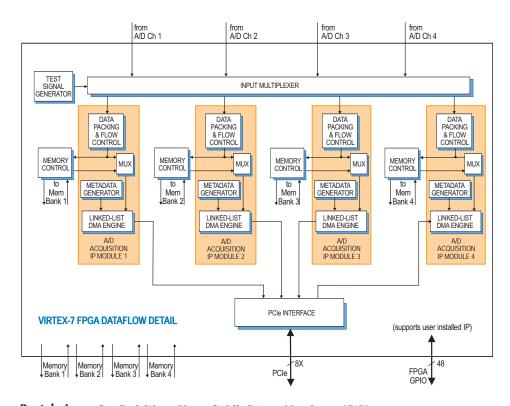

#### Features

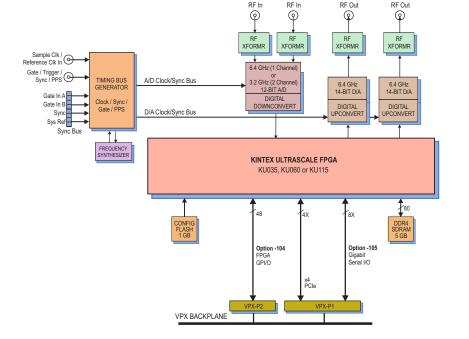

- Complete radar and software radio interface solution

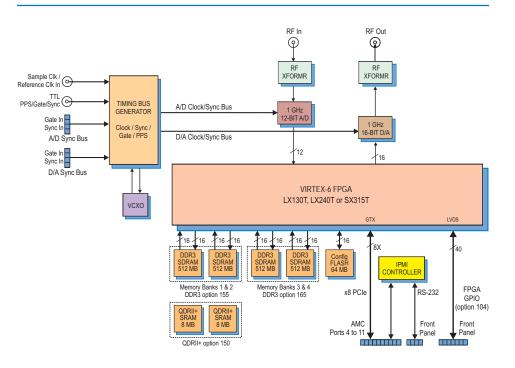

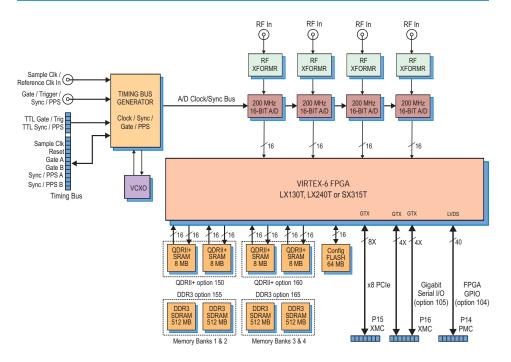

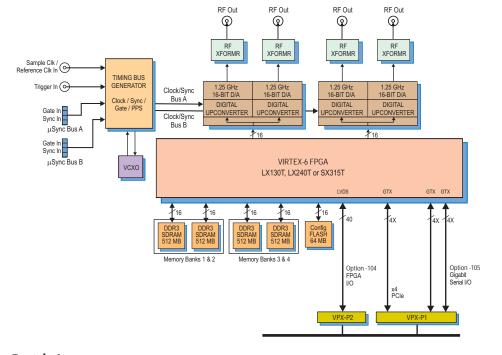

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- One 1 GHz 12-bit A/D

- One 1 GHz 16-bit D/A

- Up to 2 GB of DDR3 SDRAM or 16 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

- Dual-µSync clock/sync bus for multimodule synchronization

- PCI Express (Gen. 1 & 2) interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

#### **General Information**

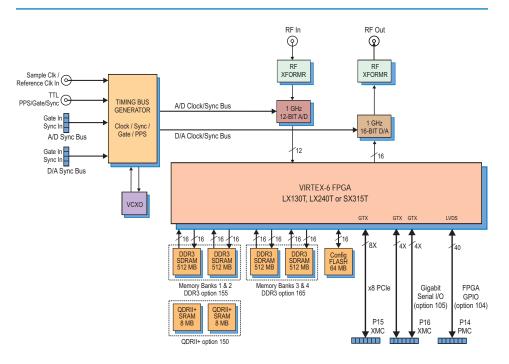

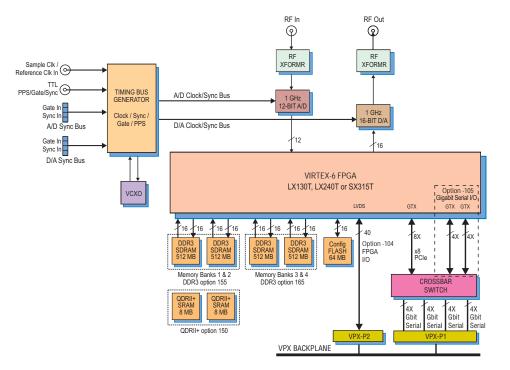

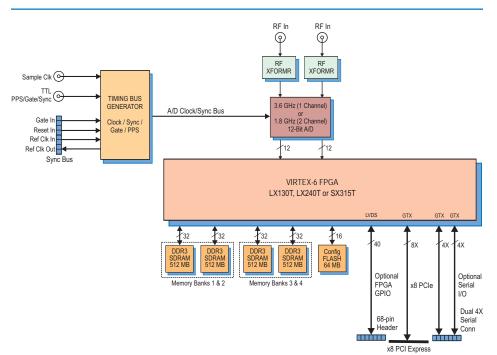

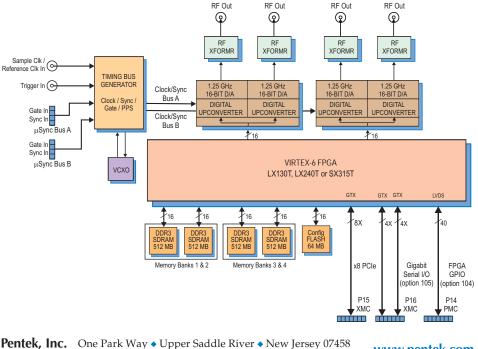

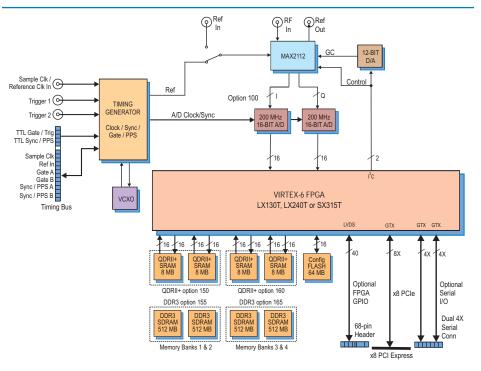

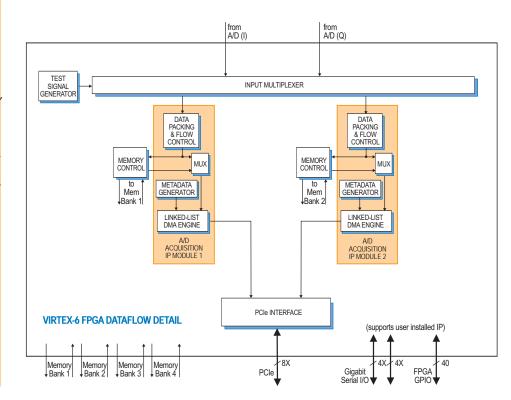

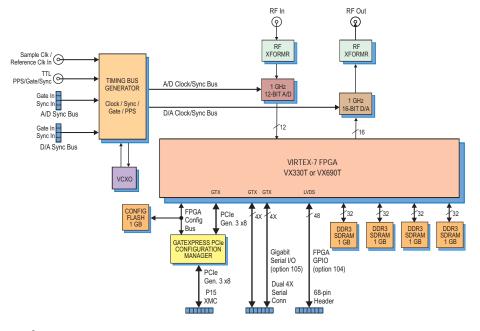

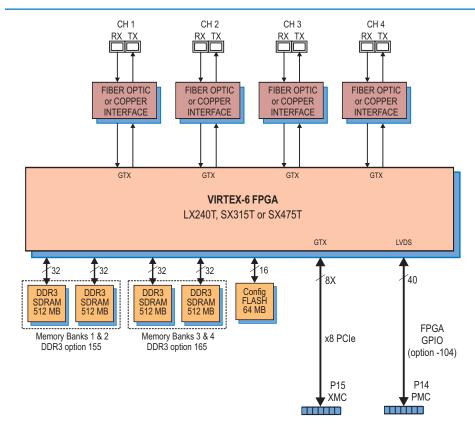

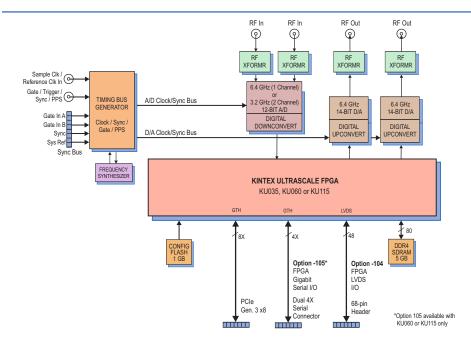

Model 71630 is a member of the Cobalt<sup>®</sup> family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. A highspeed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture and playback features offer an ideal turnkey solution as well as a platform for developing and deploying custom FPGA processing IP.

It includes 1 GHz A/D and D/A converters and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71630 includes optional general purpose and gigabit serial card connectors for application-specific I/O.

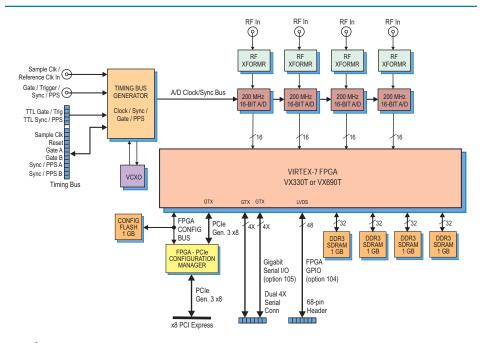

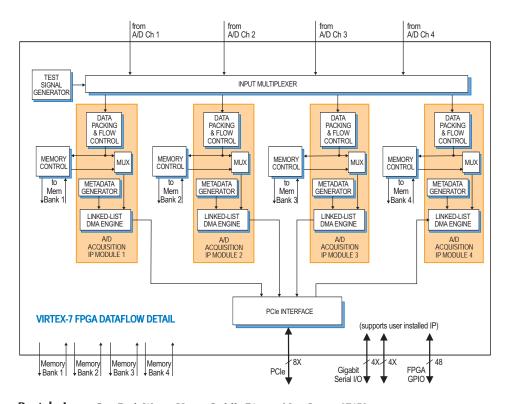

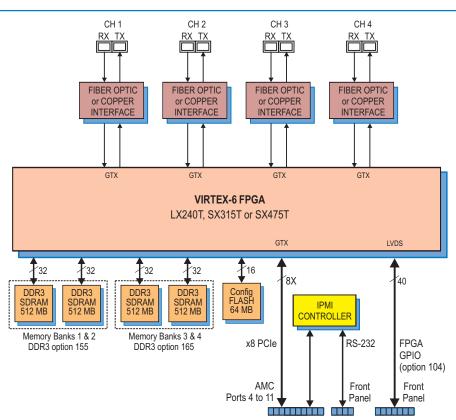

#### The Cobalt Architecture

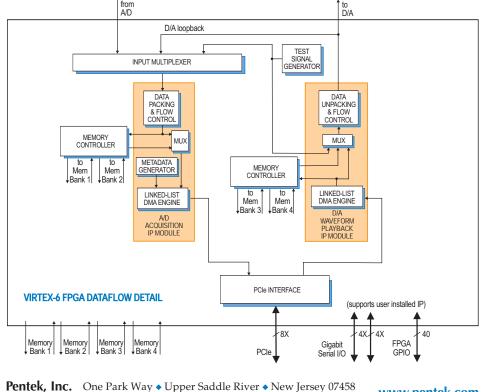

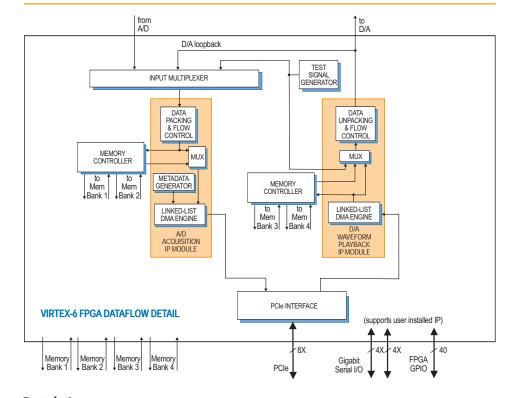

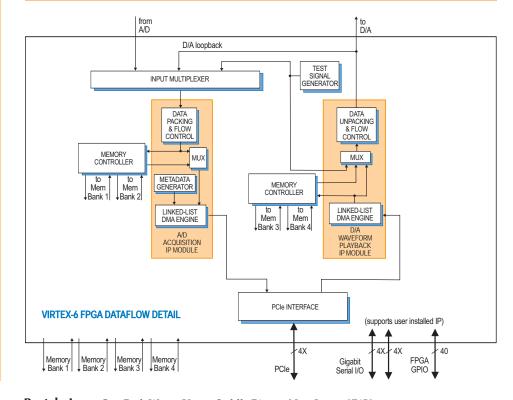

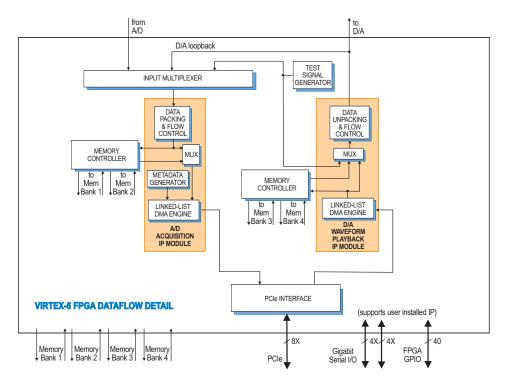

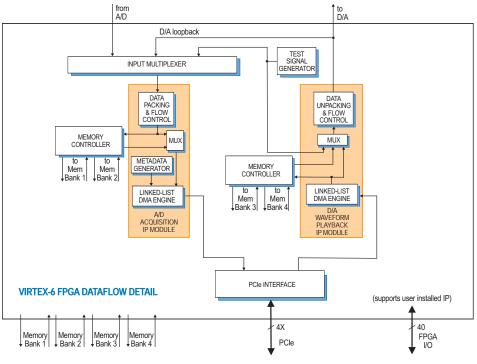

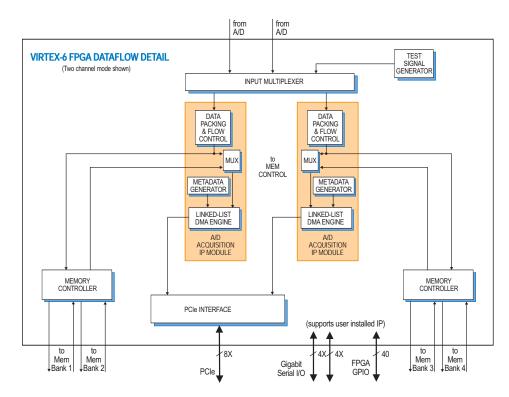

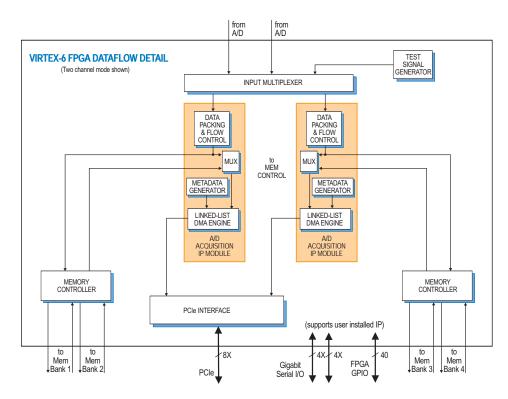

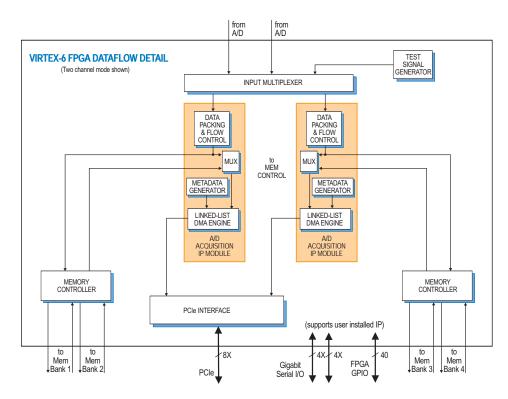

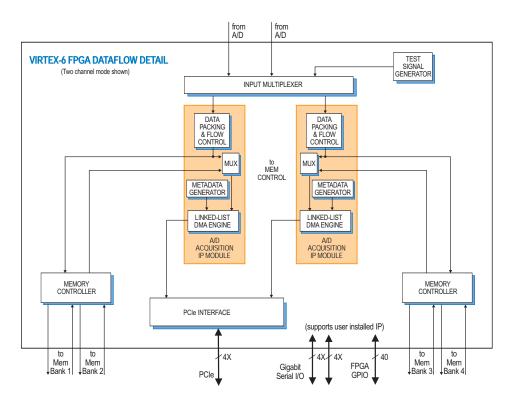

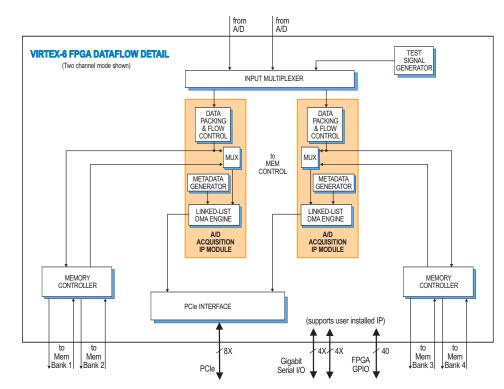

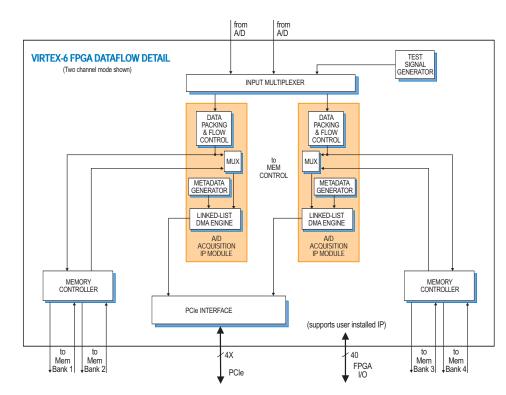

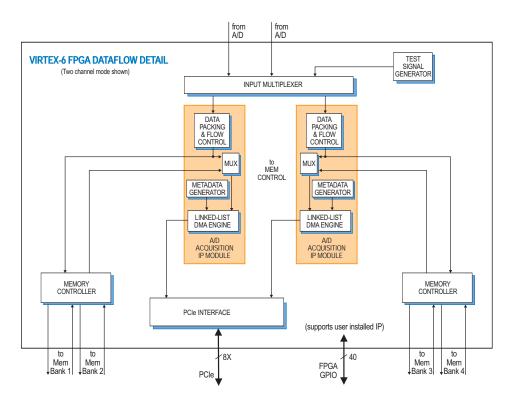

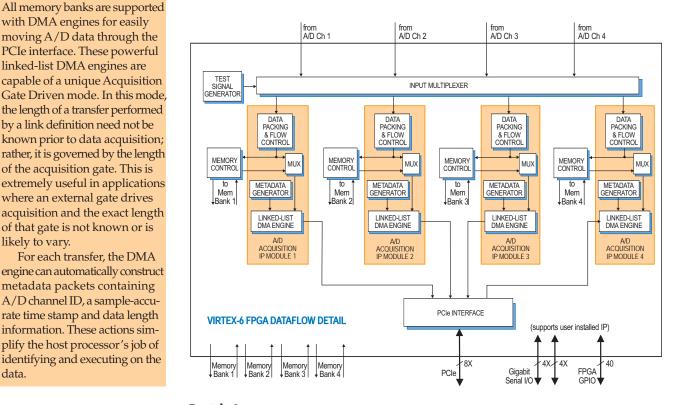

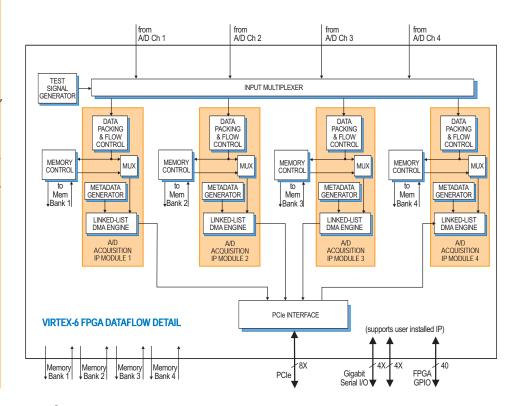

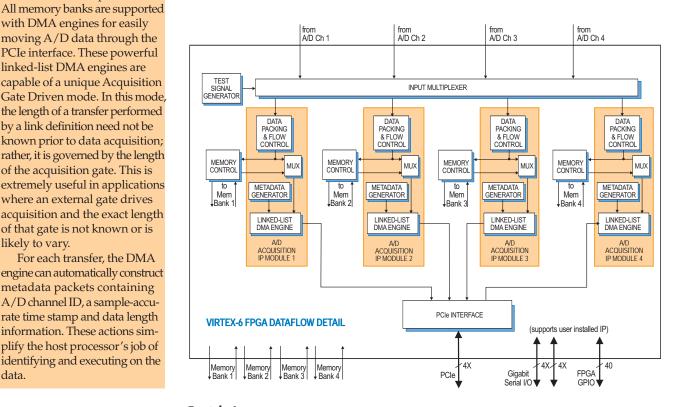

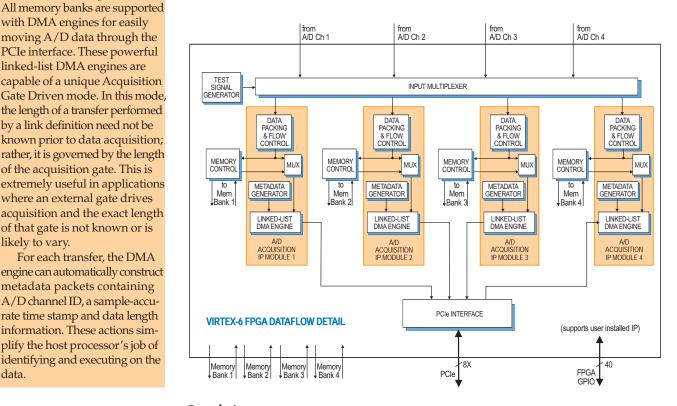

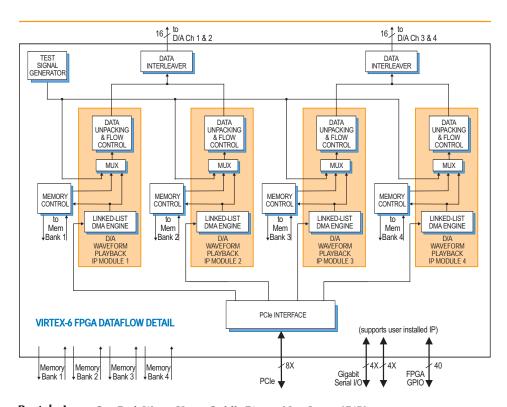

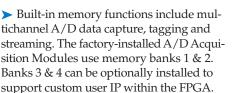

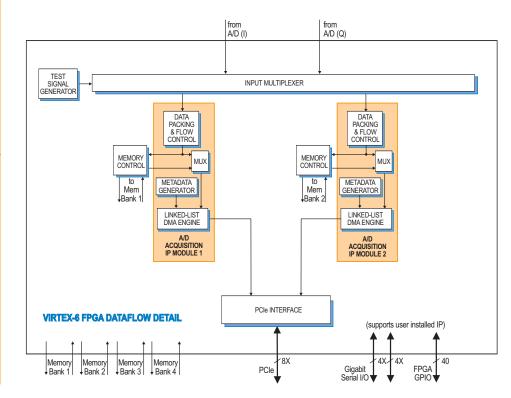

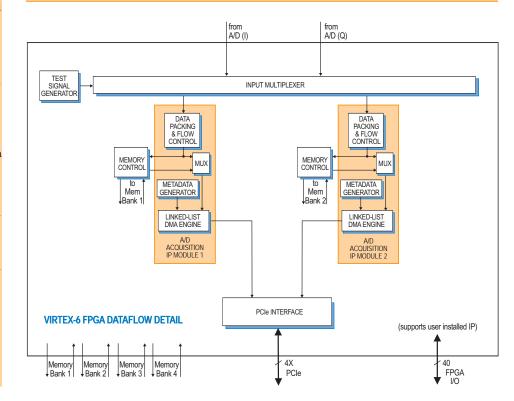

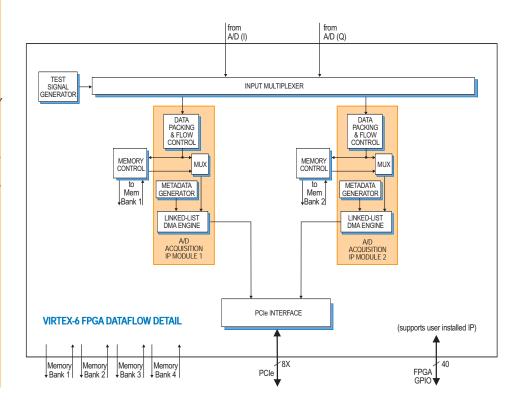

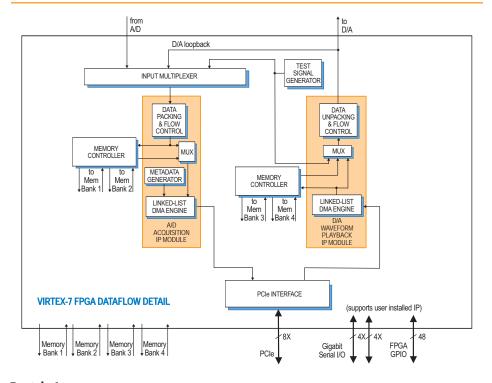

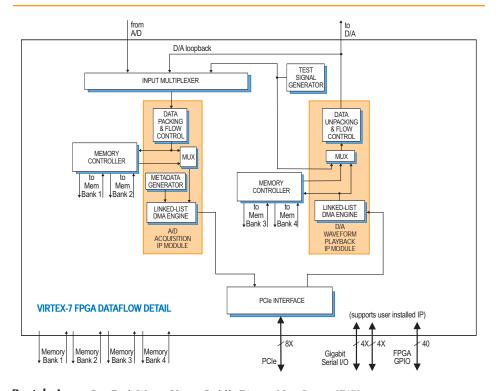

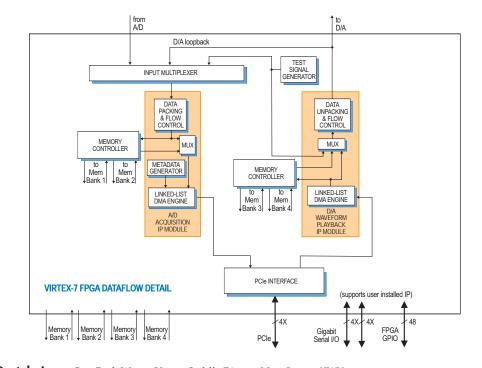

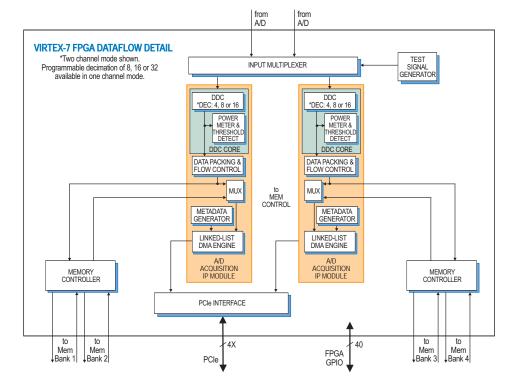

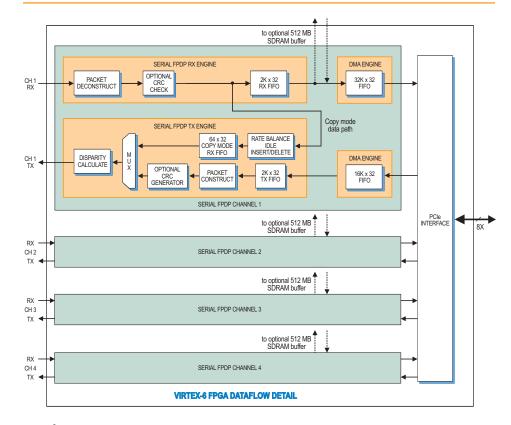

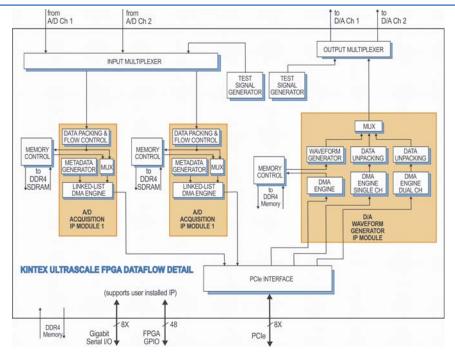

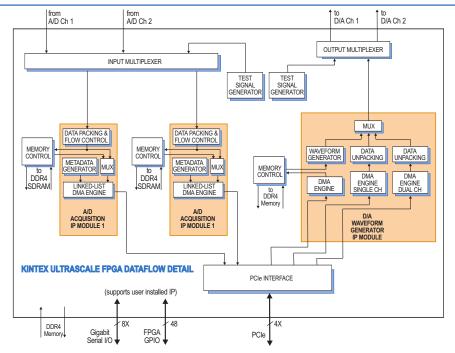

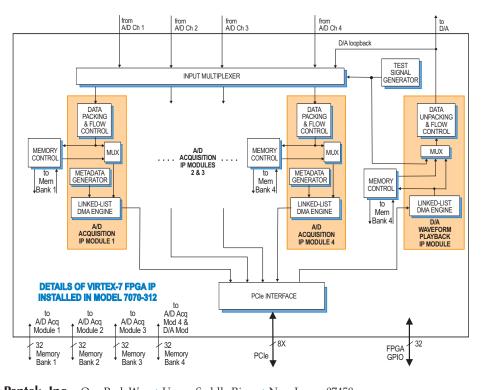

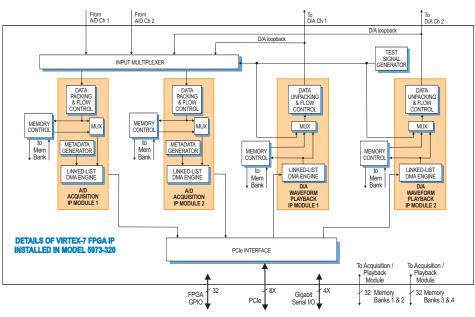

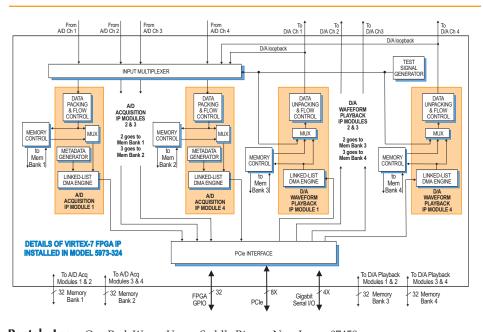

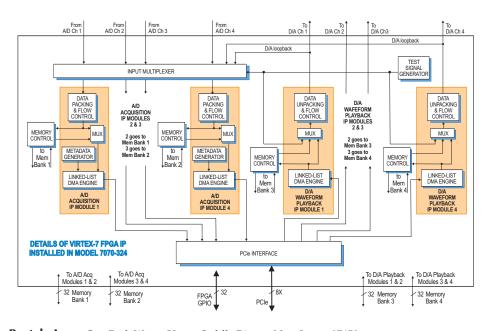

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 71630 factory-installed functions include an A/D acquisition and a D/A waveform playback IP module. In addition, IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 71630 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

#### **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

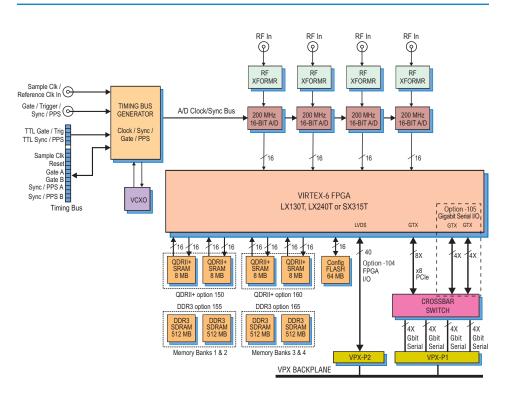

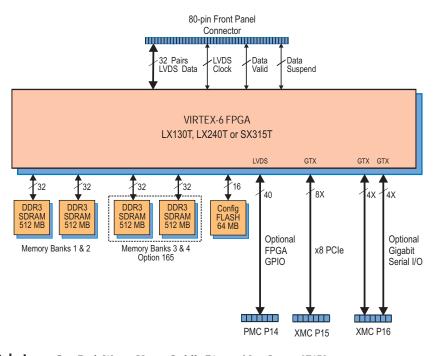

#### **Xilinx Virtex-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

Option -104 installs the P14 PMC connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

Option -105 installs the P16 XMC connector with one 8X or two 4X gigabit links to the FPGA to support serial protocols.

Pentek, Inc. One Park Way Upper Saddle River New Jersey 07458 Tel: 201·818·5900 Fax: 201·818·5904 Email: info@pentek.com

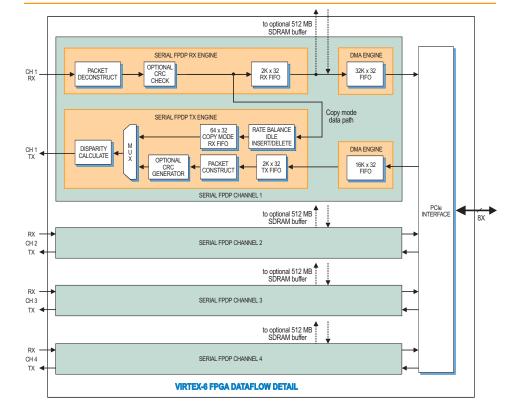

The 71630 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

#### D/A Waveform Playback IP Module

The Model 71630 factoryinstalled functions include a sophisticated D/A Waveform Playback IP module. A linkedlist controller allows users to easily play back waveforms stored in either on-board memory or off-board host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

#### A/D Converter Stage

The front end accepts an analog HF or IF input on a front panel SSMC connector with transformer coupling into a Texas Instruments ADS5400 1 GHz, 12-bit A/D converter.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

#### D/A Converter Stage

The 71630 features a TI DAC5681Z 1 GHz, 16-bit D/A. The converter has an input sample rate of 1 GSPS, allowing it to acept full rate data from the FPGA. Additionally, the D/A includes a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4 rate input data. Analog output is through a front panel SSMC connector.

#### **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives a sample clock either from the front panel SSMC connector or from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this latter mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the VCXO. Either clock source (front panel or VCXO) can be used directly or can be divided independently by 2, 4, 8, or 16 to provide different lower frequency A/D and D/A clocks.

A pair of front panel  $\mu$ Sync connectors allows multiple modules to be synchronized. They accept CML inputs that drive the board's sync and gate/trigger signals.

The Pentek Model 7192 and Model 9192 Cobalt Synchronizers can drive multiple 71630 µSync connectors enabling large, multichannel synchronous configurations. Also, an LVTTL external gate/trigger input is accepted on a front panel SSMC connector.

#### **Memory Resources**

The 71630 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory. Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the module's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes. >

www.pentek.com

Tel: 201.818.5900 Fax: 201.818.5904 Email: info@pentek.com

#### **Model 8266**

The Model 8266 is a fullyintegrated PC development system for Pentek Cobalt and Onyx PCI Express boards (Models 78xxx). It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

#### **Ordering Information**

| Model                            | Description             |

|----------------------------------|-------------------------|

| 71630                            | 1 GHz A/D and D/A,      |

|                                  | Virtex-6 FPGA - XMC     |

| <b>Options:</b>                  |                         |

| -002*                            | -2 FPGA speed grade     |

| -062                             | XC6VLX240T FPGA         |

| -064                             | XC6VSX315T FPGA         |

| -104                             | LVDS FPGA I/O through   |

|                                  | P14 connector           |

| -105                             | Gigabit serial FPGA I/O |

|                                  | through P16 connector   |

| -150                             | Two 8 MB QDRII+ SRAM    |

|                                  | Memory Banks            |

|                                  | (Banks 1 and 2)         |

| -155                             | Two 512 MB DDR3         |

|                                  | SDRAM Memory Banks      |

|                                  | (Banks 1 and 2)         |

| -165                             | Two 512 MB DDR3         |

|                                  | SDRAM Memory Banks      |

|                                  | (Banks 3 and 4)         |

| * This option is always required |                         |

Contact Pentek for availability of rugged and conduction-cooled versions

#### Model Description 8266 PC Developmen

8266 PC Development System See 8266 Datasheet for Options

#### ► XMC Interface

The Model 71630 complies with the VITA 42.0 XMC specification. Two connectors each provide dual 4X links or a single 8X link with up to a 6 GHz bit clock. With dual XMC connectors, the 71630 supports x8 PCIe on the first XMC connector leaving the second connector free to support user-installed transfer protocols specific to the target application.

#### **PCI Express Interface**

The Model 71630 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the module.

#### **Specifications**

Front Panel Analog Signal Inputs Input Type: Transformer-coupled, front panel female SSMC connectors A/D Converter Type: Texas Instruments ADS5400 Sampling Rate: 100 MHz to 1 GHz Resolution: 12 bits **D/A Converter** Type: Texas Instruments DAC5681Z Input Data Rate: 1 GHz max. **Interpolation Filter:** bypass, 2x or 4x Output Sampling Rate: 1 GHz max. Resolution: 16 bits Front Panel Analog Signal Outputs Output Type: Transformer-coupled, front panel female SSMC connectors

Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

Clock Synthesizer Clock Source: Selectable from on-board programmable VCXO or front panel external clock VCXO Frequency Ranges: 10 to 945

MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phaselocked to an external 4 to 200 MHz system reference, typically 10 MHz **Clock Dividers:** External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

#### **External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

Timing Bus: 19-pin µSync bus connector includes sync and gate/trigger inputs, CML

#### **External Trigger Input**

**Type:** Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

Field Programmable Gate Array Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2 or XC6VSX315T-2 Custom I/O

**Option -104:** Installs the PMC P14 connector with 20 LVDS pairs to the FPGA **Option -105:** Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the FPGA

Memory

Option 150: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR Option 155 or 165: Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

**PCI-Express Interface**

PCI Express Bus: Gen.1: x4 or x8; Gen 2: x4

Environmental

**Operating Temp:** 0° to 50° C

Storage Temp: –20° to 90° C

**Relative Humidity:** 0 to 95%, non-cond. **Size:** Standard XMC module, 2.91 in. x 5.87 in.

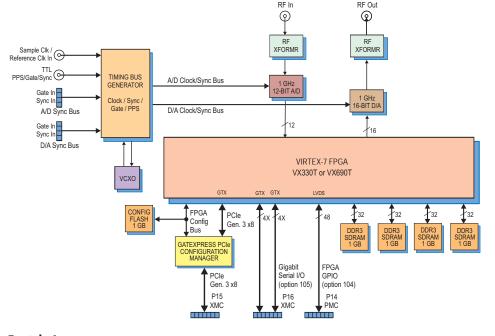

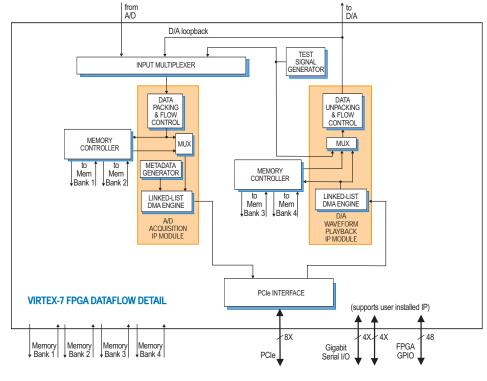

#### **Features**

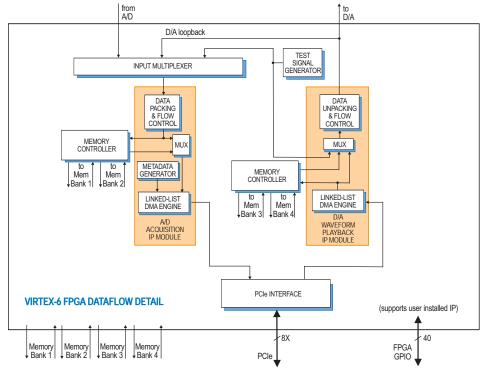

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- One 1 GHz 12-bit A/D

- One 1 GHz 16-bit D/A

- Up to 2 GB of DDR3 SDRAM or 16 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

- Dual-µSync clock/sync bus for multimodule synchronization

- PCI Express (Gen. 1 & 2) interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

#### **General Information**

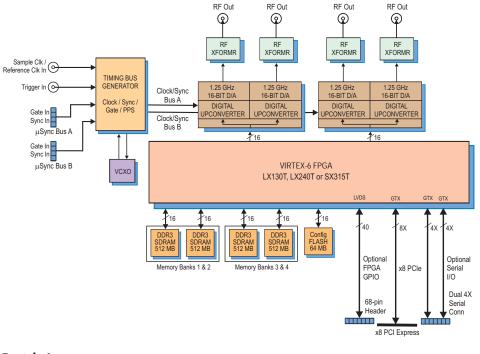

Model 78630 is a member of the Cobalt<sup>®</sup> family of high performance PCIe boards based on the Xilinx Virtex-6 FPGA. A highspeed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture and playback features offer an ideal turnkey solution as well as a platform for developing and deploying custom FPGA processing IP.

It includes 1 GHz A/D and 1 GHz D/A converters and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 78630 includes optional general-purpose and gigabit serial card connectors for application specific I/O protocols.

#### The Cobalt Architecture

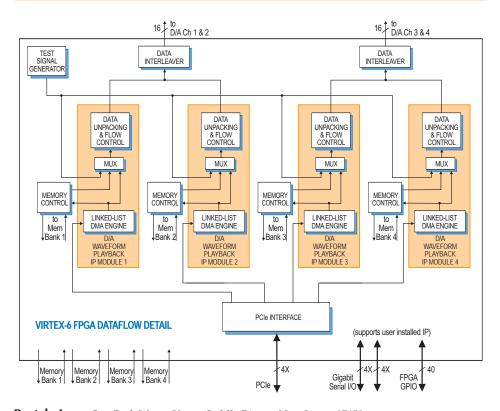

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory installed applications ideally matched to the board's analog interfaces. The 78630 factory-installed functions include an A/D acquisition and a D/A waveform playback IP module. In addition, IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 78630 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

#### **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

#### **Xilinx Virtex-6 FPGA**

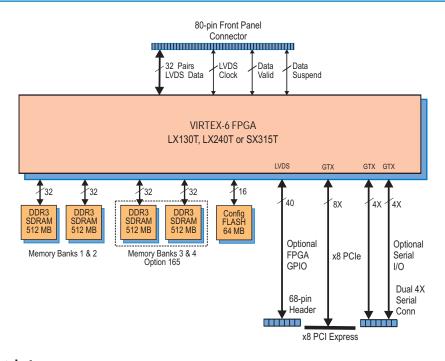

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

Option -104 connects 20 pairs of LVDS signals from the FPGA on PMC P14 to a 68-pin DIL ribbon-cable header on the PCIe board for custom I/O.

Option -105 connects two 4X gigabit serial links from the FPGA on XMC P16 to two 4X gigabit serial connectors along the top edge of the PCIe board. >

Pentek, Inc. One Park Way

Upper Saddle River

New Jersey 07458

Tel: 201-818-5900

Fax: 201-818-5904

Email: info@pentek.com

The 78630 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

#### D/A Waveform Playback IP Module

The Model 78630 factoryinstalled functions include a sophisticated D/A Waveform Playback IP module. A linkedlist controller allows users to easily play back waveforms stored in either on-board memory or off- board host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

#### A/D Converter Stage

The front end accepts an analog HF or IF input on a front panel SSMC connector with transformer coupling into a Texas Instruments ADS5400 1 GHz, 12-bit A/D converter.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other board resources.

#### D/A Converter Stage

The 78630 features a TI DAC5681Z 1 GHz, 16-bit D/A. The converter has an input sample rate of 1 GSPS, allowing it to acept full rate data from the FPGA. Additionally, the D/A includes a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4 rate input data. Analog output is through a front panel SSMC connector.

#### **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives a sample clock either from the front panel SSMC connector or from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this latter mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the VCXO. Either clock source (front panel or VCXO) can be used directly or can be divided independently by 2, 4, 8, or 16 to provide different lower frequency A/D and D/A clocks.

A pair of front panel  $\mu$ Sync connectors allows multiple boards to be synchronized. They accept CML inputs that drive the board's sync and gate/trigger signals.

The Pentek Model 7892 and Model 9192 Cobalt Synchronizers can drive multiple 78630 µSync connectors enabling large, multichannel synchronous configurations. Also, an LVTTL external gate/trigger input is accepted on a front panel SSMC connector.

#### **Memory Resources**

The 78630 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory. Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the board's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes. >

www.pentek.com

**Pentek, Inc.** One Park Way • Upper Saddle River • New Jersey 07458

Tel: 201.818.5900 Fax: 201.818.5904 Email: info@pentek.com

Model 8266 The Model 8266 is a fullyintegrated PC development system for Pentek Cobalt and Onyx PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

#### **Ordering Information**

|                                  | -                                                                |  |

|----------------------------------|------------------------------------------------------------------|--|

| Model                            | Description                                                      |  |

| 78630                            | 1 GHz A/D and D/A,                                               |  |

|                                  | Virtex-6 FPGA - x8 PCIe                                          |  |

| Options:                         |                                                                  |  |

| -002*                            | -2 FPGA speed grade                                              |  |

| -062                             | XC6VLX240T                                                       |  |

| -064                             | XC6VSX315T                                                       |  |

| -104                             | LVDS FPGA I/O through<br>68-pin ribbon cable<br>connector        |  |

| -105                             | Gigabit serial FPGA I/O<br>through two 4X top edge<br>connectors |  |

| -150                             | Two 8 MB QDRII+<br>SRAM Memory Banks<br>(Banks 1 and 2)          |  |

| -155                             | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2)         |  |

| -165                             | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4)         |  |

| * This option is always required |                                                                  |  |

\* This option is always required

#### Model Description

8266 PC Development System See 8266 Datasheet for Options

#### **PCI Express Interface**

The Model 78630 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the board.

#### **Specifications**

Front Panel Analog Signal Inputs Input Type: Transformer-coupled, front panel female SSMC connectors

A/D Converter Type: Texas Instruments ADS5400 Sampling Rate: 100 MHz to 1 GHz Resolution: 12 bits

D/A Converter Type: Texas Instruments DAC5681Z Input Data Rate: 1 GHz max. Interpolation Filter: bypass, 2x or 4x Output Sampling Rate: 1 GHz max.

Resolution: 16 bits Front Panel Analog Signal Outputs Output Type: Transformer-coupled, front panel female SSMC connectors

Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

Clock Synthesizer

**Clock Source:** Selectable from on-board programmable VCXO or front panel external clock

**VCXO Frequency Ranges**: 10 to 945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phaselocked to an external 4 to 200 MHz system reference, typically 10 MHz **Clock Dividers:** External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

#### **External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

Timing Bus: 19-pin μSync bus connector includes sync and gate/trigger inputs, CML

**External Trigger Input**

**Type:** Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

Field Programmable Gate Array Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2, or XC6VSX315T-2

Custom I/O

**Option -104:** Connects 20 pairs of LVDS signals from the FPGA on PMC P14 to a 68-pin DIL ribbon-cable header on the PCIe board for custom I/O. **Option -105:** Connects two 4X gigabit

serial links from the FPGA on XMC P16 to two 4X gigabit serial connectors along the top edge of the PCIe board

Memory

**Option 150:** Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR **Option 155 or 165:** Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

**PCI-Express Interface**

PCI Express Bus: Gen.1: x4 or x8 Gen. 2: x4

Environmental

**Operating Temp:** 0° to 50° C

**Storage Temp:** –20° to 90° C

**Relative Humidity:** 0 to 95%, non-cond. **Size:** Half length PCIe card, 4.38 in. x 7.13 in.

Model 53630 COTS (left) and rugged version

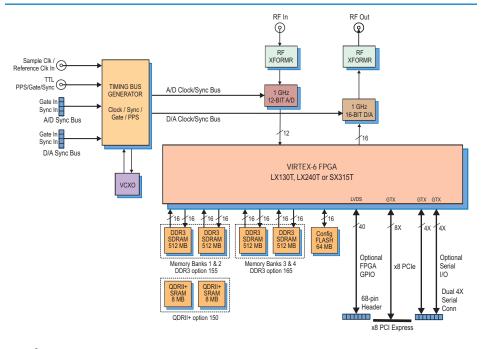

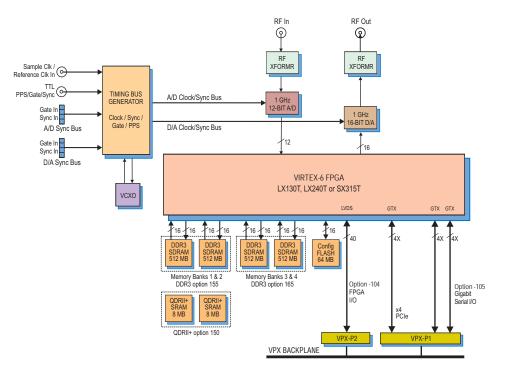

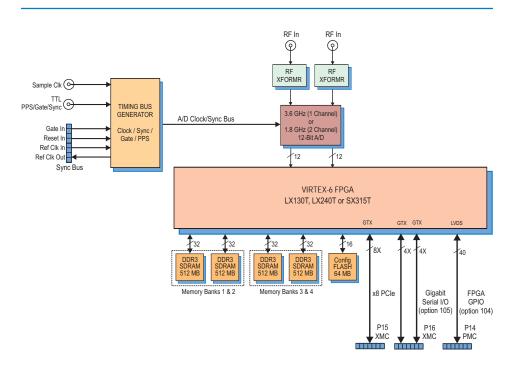

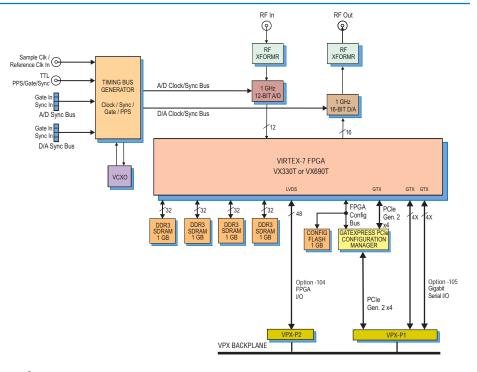

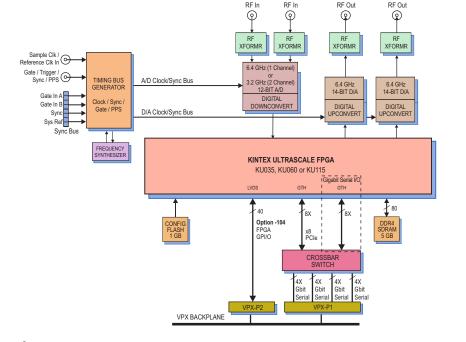

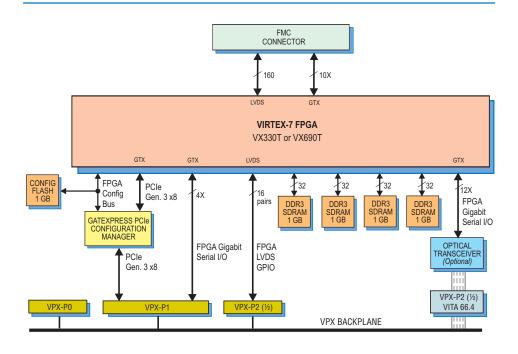

#### **Features**

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- Supports gigabit serial fabrics including PCI Express, Serial RapidIO and Xilinx Aurora

- One 1 GHz 12-bit A/D

- One 1 GHz 16-bit D/A

- Up to 2 GB of DDR3 SDRAM or 16 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

- Dual-µSync clock/sync bus for multiboard synchronization

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

- 3U VPX form factor provides a compact, rugged platform

- Compatible with several VITA standards including: VITA-46, VITA-48 and VITA-65 (OpenVPX<sup>TM</sup> System Specification)

- Ruggedized and conductioncooled versions available

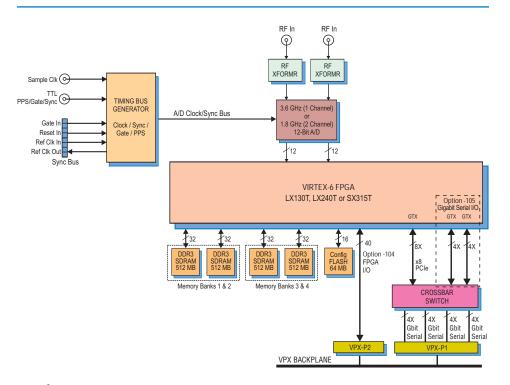

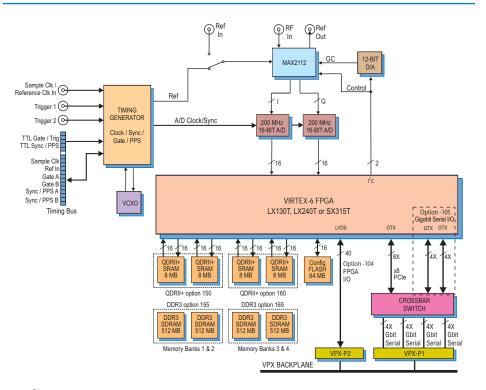

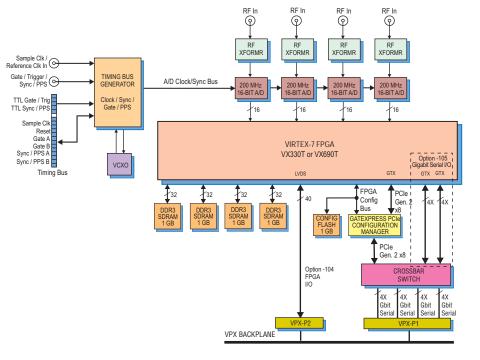

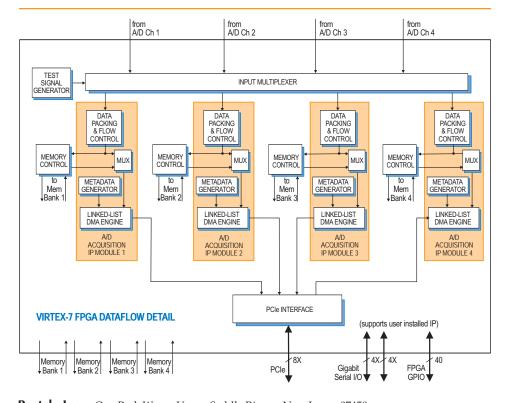

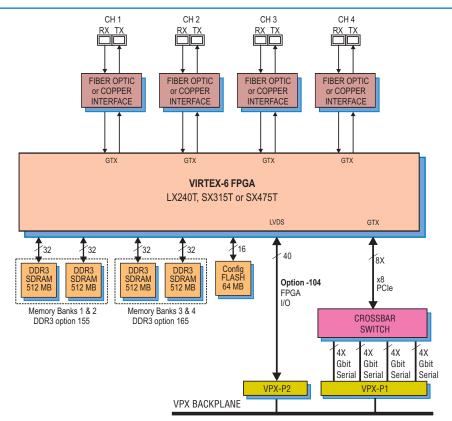

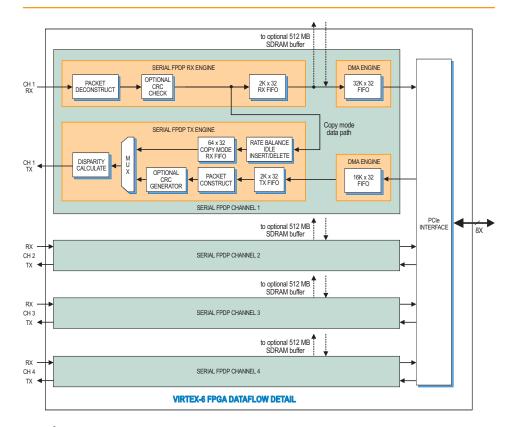

#### **General Information**

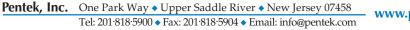

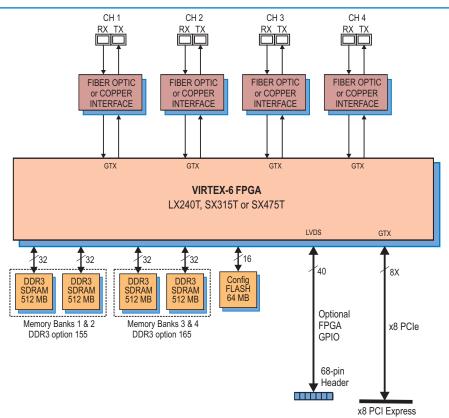

Model 53630 is a member of the Cobalt<sup>®</sup> family of high performance 3U VPX boards based on the Xilinx Virtex-6 FPGA. A highspeed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture and playback features offer an ideal turnkey solution.

It includes 1 GHz A/D and D/A converters and four banks of memory. It features built-in support for PCI Express over the 3U VPX backplane.

#### The Cobalt Architecture

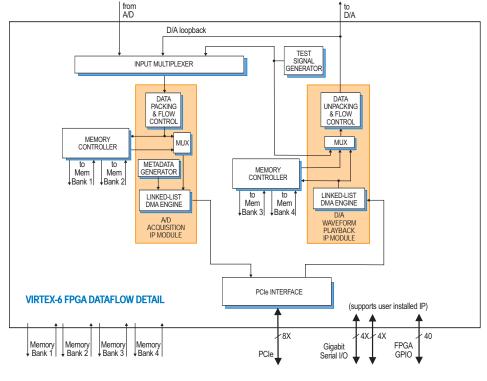

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 53630 factory-installed functions include an A/D acquisition and a D/A waveform playback IP module. In addition, IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 53630 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

#### **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

#### **Xilinx Virtex-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

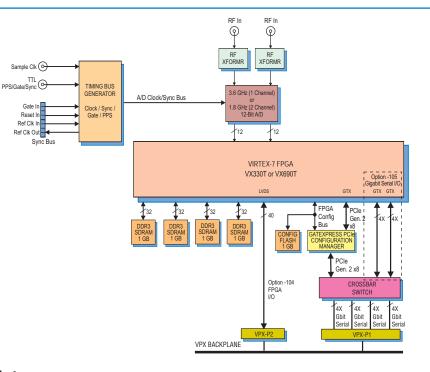

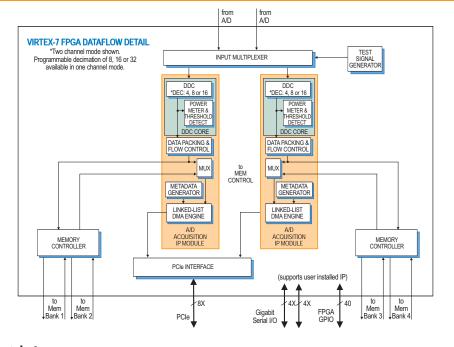

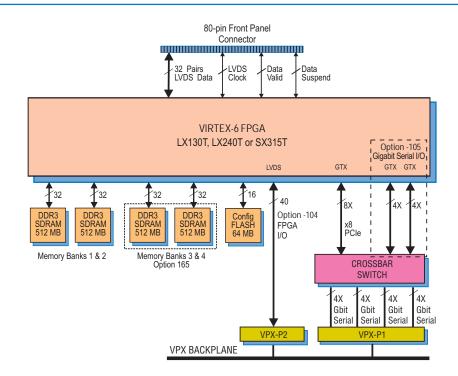

Option -104 provides 20 pairs of LVDS connections between the FPGA and the VPX P2 connector for custom I/O.

Option -105 provides one 8X or two 4X gigabit links between the FPGA and the VPX P1 connector to support serial protocols. >

Pentek, Inc. One Park Way

Upper Saddle River

New Jersey 07458

Tel: 201-818-5900

Fax: 201-818-5904

Email: info@pentek.com

The 53630 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

#### D/A Waveform Playback IP Module

The Model 53630 factoryinstalled functions include a sophisticated D/A Waveform Playback IP module. A linkedlist controller allows users to easily play back waveforms stored in either on-board memory or off- board host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

#### ► A/D Converter Stage

The front end accepts an analog HF or IF input on a front panel SSMC connector with transformer coupling into a Texas Instruments ADS5400 1 GHz, 12-bit A/D converter.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

#### **D/A Converter Stage**

The 53630 features a TI DAC5681Z 1 GHz, 16-bit D/A. The converter has an input sample rate of 1 GSPS, allowing it to acept full rate data from the FPGA. Additionally, the D/A includes a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4 rate input data. Analog output is through a front panel SSMC connector.

#### **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives a sample clock either from the front panel SSMC connector or from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this latter mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the VCXO. Either clock source (front panel or VCXO) can be used directly or can be divided independently by 2, 4, 8, or 16 to provide different lower frequency A/D and D/A clocks.

A pair of front panel  $\mu$ Sync connectors allows multiple boards to be synchronized. They accept CML inputs that drive the board's sync and gate/trigger signals.

The Pentek Model 5392 and Model 9192 Cobalt Synchronizers can drive multiple 53630 µSync connectors enabling large, multichannel synchronous configurations. Also, an LVTTL external gate/trigger input is accepted on a front panel SSMC connector.

#### **Memory Resources**

The 53630 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory. Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the board's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes. >

#### **Model 8267**

The Model 8267 is a fullyintegrated VPX development system for Pentek Cobalt and Onyx VPX boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

#### **Ordering Information**

| 0                                            |

|----------------------------------------------|

| Description                                  |

| 1 GHz A/D and D/A,<br>Virtex-6 FPGA - 3U VPX |

|                                              |

| -2 FPGA speed grade                          |

| XC6VLX240T FPGA                              |

| XC6VSX315T FPGA                              |

| LVDS FPGA I/O to VPX<br>P2                   |

|                                              |

- -105 Gigabit serial FPGA I/O to VPX P1

-150 Two 8 MB QDRII+ SRAM

- Memory Banks (Banks 1 and 2)

- -155 Two 512 MB DDR3 SDRAM Memory Banks (Banks 1 and 2)

- -165 Two 512 MB DDR3 SDRAM Memory Banks (Banks 3 and 4)

\* This option is always required

Contact Pentek for availability of rugged and conduction-cooled versions

#### Model Description

8267 VPX Development System. See 8267 Datasheet for Options

#### ► PCI Express Interface

The Model 53630 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the board.

#### Fabric-Transparent Crossbar Switch

The 53630 features a unique high-speed switching configuration. A fabric-transparent crossbar switch bridges numerous interfaces and components on the board using gigabit serial data paths with no latency. Programmable signal input equalization and output pre-emphasis settings enable optimization. Data paths can be selected as single (1X) lanes, or groups of four lanes (4X).

#### **Specifications**

Front Panel Analog Signal Inputs Input Type: Transformer-coupled, front panel female SSMC connectors

A/D Converter Type: Texas Instruments ADS5400 Sampling Rate: 100 MHz to 1 GHz Resolution: 12 bits

D/A Converter

**Type:** Texas Instruments DAC5681Z **Input Data Rate:** 1 GHz max. **Interpolation Filter:** bypass, 2x or 4x **Output Sampling Rate:** 1 GHz max. **Resolution:** 16 bits

Front Panel Analog Signal Outputs Output Type: Transformer-coupled, front panel female SSMC connectors Sample Clock Sources: On-board clock

synthesizer generates two clocks: one A/D clock and one D/A clock

Clock Synthesizer Clock Source: Selectable from on-board programmable VCXO or front panel external clock

**VCXO Frequency Ranges**: 10 to 945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phaselocked to an external 4 to 200 MHz system reference, typically 10 MHz **Clock Dividers:** External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A

clock External Clock

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

Timing Bus: 19-pin µSync bus connector includes sync and gate/trigger inputs, CML

#### **External Trigger Input**

**Type:** Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

Field Programmable Gate Array Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2 or XC6VSX315T-2

#### Custom I/O

**Option -104:** Provides 20 pairs of LVDS connections between the FPGA and the VPX P2 connector for custom I/O **Option -105:** Provides one 8X or two 4X gigabit links between the FPGA and the VPX P1 connector to support serial protocols

#### Memory

Option 150: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR Option 155 or 165: Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

PCI-Express Interface

**PCI Express Bus:** Gen.1: x4 or x8; Gen 2: x4

#### Environmental

**Operating Temp:** 0° to 50° C **Storage Temp:** -20° to 90° C **Relative Humidity:** 0 to 95%, non-cond.

Size: 3.937 in. x 6.717 in. (100 mm x 170.6 mm)

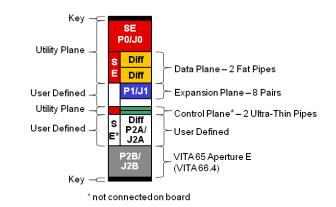

#### **VPX Families**

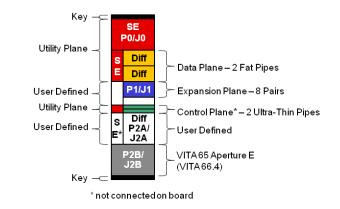

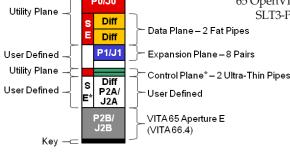

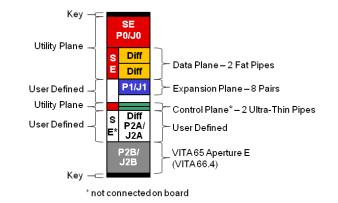

Pentek offers two families of 3U VPX products: the 53xxx and the 52xxx. For more information on a 52xxx product, please refer to the product datasheet. The table below provides a comparison of their main features.

#### **VPX Family Comparison**

|                  |                               | •                                   |

|------------------|-------------------------------|-------------------------------------|

|                  | 52xxx                         | 53xxx                               |

| Form Factor      | 3U '                          | VPX                                 |

| # of XMCs        | One                           | XMC                                 |

| Crossbar Switch  | No                            | Yes                                 |

| PCIe path        | VPX P1                        | VPX P1 or P2                        |

| PCIe width       | x4                            | x8                                  |

| Option -104 path | 20 pairs c                    | n VPX P2                            |

| Option -105 path | Two x4 or one x8<br>on VPX P1 | Two x4 or one x8<br>on VPX P1 or P2 |

| Lowest Power     | Yes                           | No                                  |

| Lowest Price     | Yes                           | No                                  |

Model 52630 COTS (left) and rugged version

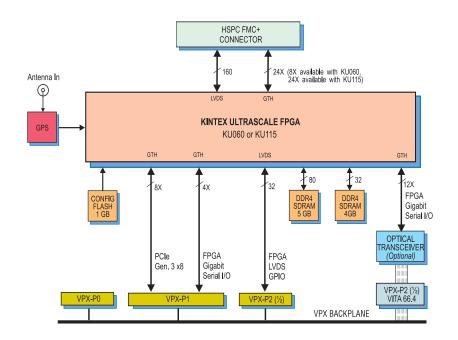

#### **Features**

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- Supports gigabit serial fabrics including PCI Express, Serial RapidIO and Xilinx Aurora

- One 1 GHz 12-bit A/D

- One 1 GHz 16-bit D/A

- Up to 2 GB of DDR3 SDRAM or 16 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

- Dual-µSync clock/sync bus for multiboard synchronization

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

- 3U VPX form factor provides a compact, rugged platform

- Compatible with several VITA standards including: VITA-46, VITA-48 and VITA-65 (OpenVPX<sup>TM</sup> System Specification)

- Ruggedized and conductioncooled versions available

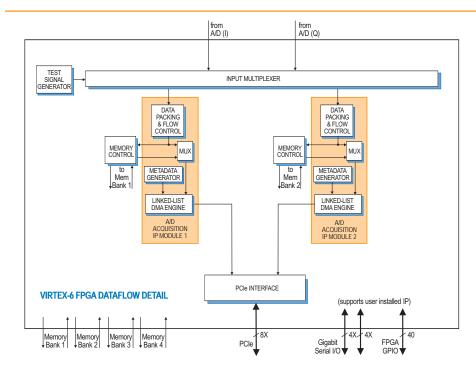

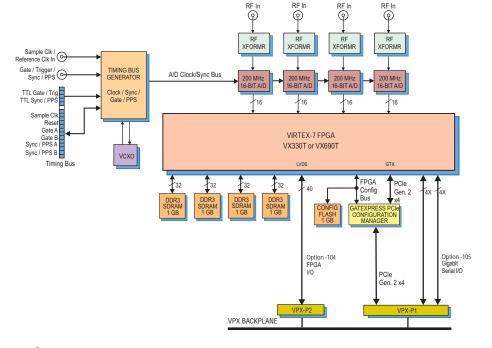

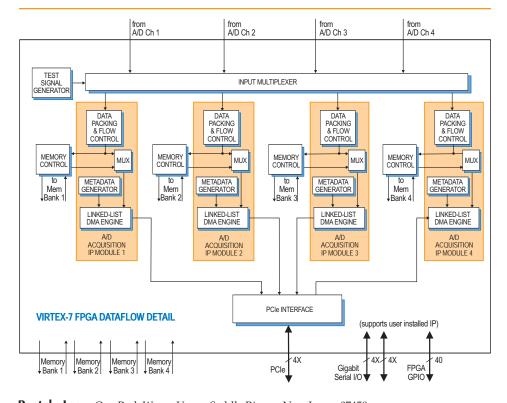

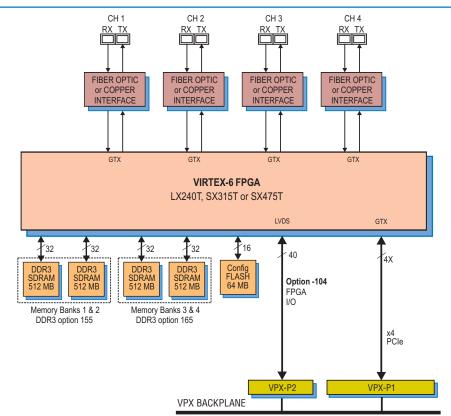

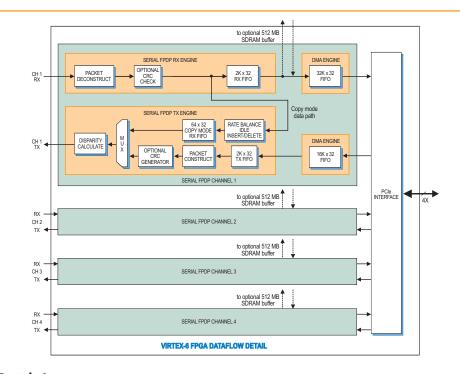

#### **General Information**

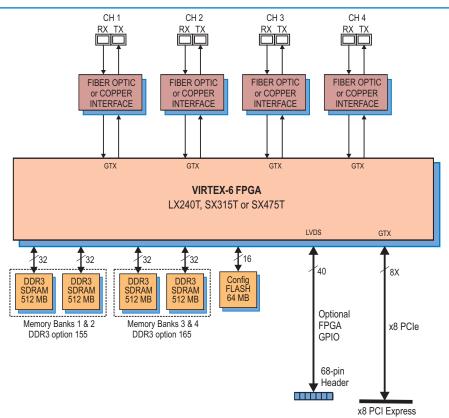

Model 52630 is a member of the Cobalt<sup>®</sup> family of high performance 3U VPX boards based on the Xilinx Virtex-6 FPGA. A highspeed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture and playback features offer an ideal turnkey solution.

It includes 1 GHz A/D and D/A converters and four banks of memory. It features built-in support for PCI Express over the 3U VPX backplane.

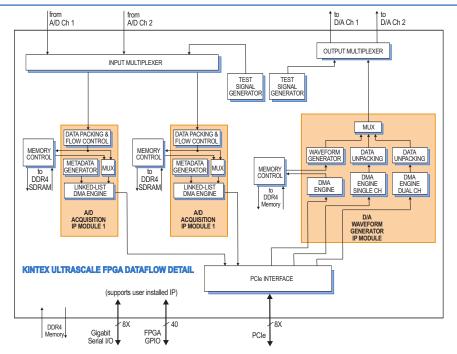

#### The Cobalt Architecture

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 52630 factory-installed functions include an A/D acquisition and a D/A waveform playback IP module. In addition, IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 52630 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

#### **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

#### Xilinx Virtex-6 FPGA

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

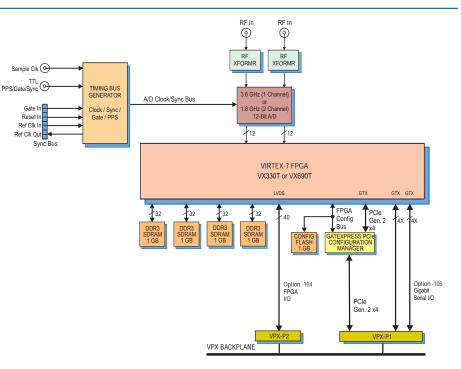

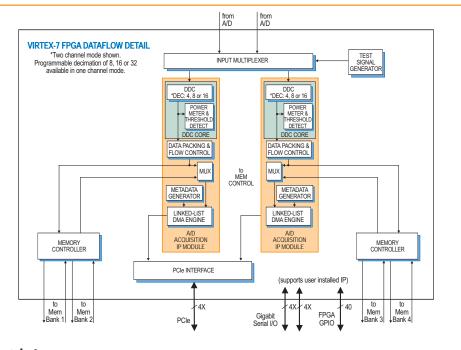

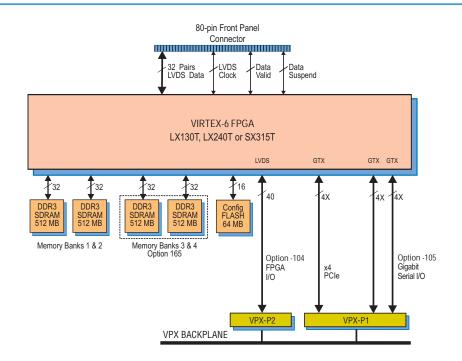

Option -104 provides 20 pairs of LVDS connections between the FPGA and the VPX P2 connector for custom I/O.

Option -105 provides one 8X or two 4X gigabit links between the FPGA and the VPX P1 connector to support serial protocols. >

Pentek, Inc. One Park Way

Upper Saddle River

New Jersey 07458

Tel: 201.818.5900

Fax: 201.818.5904

Email: info@pentek.com

The 52630 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

#### **D/A Waveform Playback IP Module**

The Model 52630 factoryinstalled functions include a sophisticated D/A Waveform Playback IP module. A linkedlist controller allows users to easily play back waveforms stored in either on-board memory or off-board host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

PENTE

A/D Converter Stage

The front end accepts an analog HF or IF input on a front panel SSMC connector with transformer coupling into a Texas Instruments ADS5400 1 GHz, 12-bit A/D converter.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

#### D/A Converter Stage

The 52630 features a TI DAC5681Z 1 GHz, 16-bit D/A. The converter has an input sample rate of 1 GSPS, allowing it to acept full rate data from the FPGA. Additionally, the D/A includes a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4rate input data. Analog output is through a front panel SSMC connector.

#### **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives a sample clock either from the front panel SSMC connector or from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this latter mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the VCXO.

Either clock source (front panel or VCXO) can be used directly or can be divided independently by 2, 4, 8, or 16 to provide different lower frequency A/D and D/A clocks.

A pair of front panel µSync connectors allows multiple modules to be synchronized. They accept CML inputs that drive the board's sync and gate/trigger signals.

The Pentek Model 5292 and Model 9192 Cobalt Synchronizers can drive multiple 52630 µSync connectors enabling large, multichannel synchronous configurations. Also, an LVTTL external gate/trigger input is accepted on a front panel SSMC connector.

#### **Memory Resources**

The 52630 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory. Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the board's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes. >

**Pentek, Inc.** One Park Way • Upper Saddle River • New Jersey 07458 Tel: 201.818.5900 Fax: 201.818.5904 Email: info@pentek.com

www.pentek.com

#### 1 GHz A/D and D/A, Virtex-6 FPGA - 3U VPX

#### ► PCI Express Interface

The Model 52630 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x4, the interface includes multiple DMA controllers for efficient transfers to and from the board.

#### **Specifications**

Front Panel Analog Signal Inputs Input Type: Transformer-coupled, front panel female SSMC connectors

A/D Converter Type: Texas Instruments ADS5400 Sampling Rate: 100 MHz to 1 GHz Resolution: 12 bits

D/A Converter

Type: Texas Instruments DAC5681Z Input Data Rate: 1 GHz max. Interpolation Filter: bypass, 2x or 4x Output Sampling Rate: 1 GHz max. Resolution: 16 bits

Front Panel Analog Signal Outputs Output Type: Transformer-coupled, front panel female SSMC connectors

Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

Clock Synthesizer Clock Source: Selectable from on-board programmable VCXO or front panel external clock

VCXO Frequency Ranges: 10 to 945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phaselocked to an external 4 to 200 MHz system reference, typically 10 MHz **Clock Dividers:** External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A (D clock and D (A

pendently for the A/D clock and D/A clock

#### External Clock

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

Timing Bus: 19-pin µSync bus connector includes sync and gate/trigger inputs, CML

#### **External Trigger Input**

**Type:** Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

Field Programmable Gate Array Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2 or XC6VSX315T-2

#### Custom I/O

**Option -104:** Provides 20 pairs of LVDS connections between the FPGA and the VPX P2 connector for custom I/O **Option -105:** Provides one 8X or two 4X gigabit links between the FPGA and the VPX P1 connector to support serial protocols

#### Memory

Option 150: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR Option 155 or 165: Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

**PCI-Express Interface**

PCI Express Bus: Gen. 1 or Gen 2: x4 Environmental

**Operating Temp:** 0° to 50° C

**Storage Temp:** –20° to 90° C

**Relative Humidity:** 0 to 95%, non-cond. **Size:** 3.937 in. x 6.717 in. (100 mm x 170.6 mm)

#### **VPX Families**

Pentek offers two families of 3U VPX products: the 52xxx and the 53xxx. For more information on a 53xxx product, please refer to the product datasheet. The table below provides a comparison of their main features.

#### **VPX Family Comparison**

|                  | •                             |                                     |

|------------------|-------------------------------|-------------------------------------|

|                  | 52xxx                         | 53xxx                               |

| Form Factor      | 3U V                          | VPX                                 |

| # of XMCs        | One                           | XMC                                 |

| Crossbar Switch  | No                            | Yes                                 |

| PCIe path        | VPX P1                        | VPX P1 or P2                        |

| PCIe width       | x4                            | x8                                  |

| Option -104 path | 20 pairs o                    | n VPX P2                            |

| Option -105 path | Two x4 or one x8<br>on VPX P1 | Two x4 or one x8<br>on VPX P1 or P2 |

| Lowest Power     | Yes                           | No                                  |

| Lowest Price     | Yes                           | No                                  |

#### <u>Model 8267</u>

The Model 8267 is a fullyintegrated VPX development system for Pentek Cobalt and Onyx VPX boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

#### **Ordering Information**

|          | •                                                        |

|----------|----------------------------------------------------------|

| Model    | Description                                              |

| 52630    | 1 GHz A/D and D/A,                                       |

|          | Virtex-6 FPGA - 3U VPX                                   |

| Options: |                                                          |

| -002*    | -2 FPGA speed grade                                      |

| -062     | XC6VLX240T FPGA                                          |

| -064     | XC6VSX315T FPGA                                          |

| -104     | LVDS FPGA I/O to VPX<br>P2                               |

| -105     | Gigabit serial FPGA I/O to VPX P1                        |

| -150     | Two 8 MB QDRII+ SRAM<br>Memory Banks<br>(Banks 1 and 2)  |

| -155     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2) |

| -165     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4) |

\* This option is always required

Contact Pentek for availability of rugged and conduction-cooled versions

#### Model Description

8267 VPX Development System. See 8267 Datasheet for Options

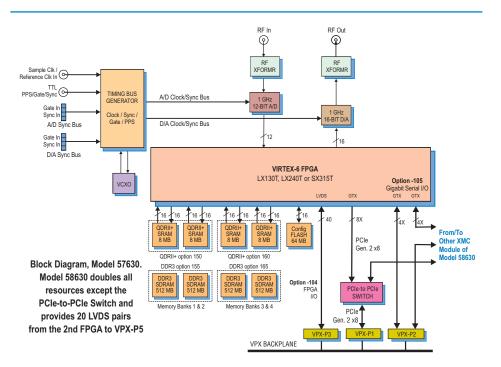

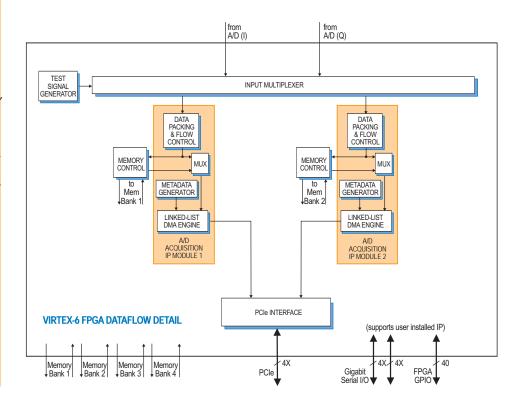

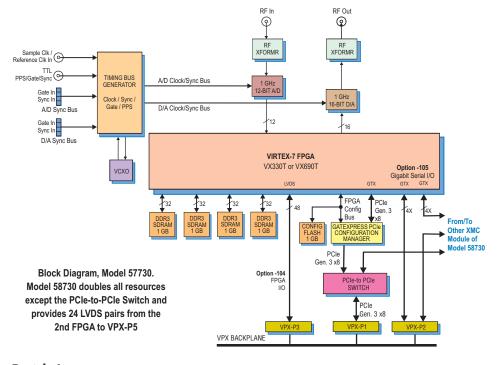

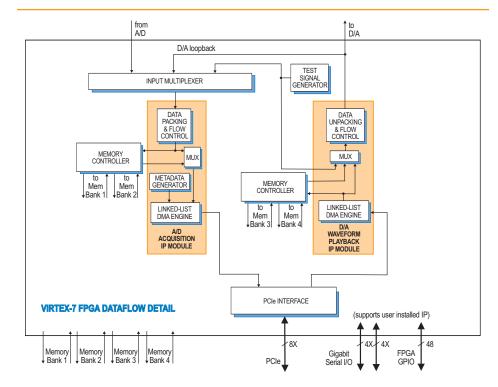

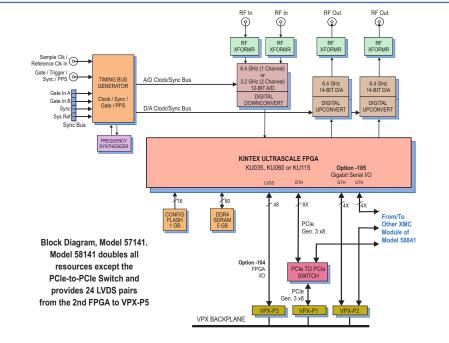

#### Models 57630 & 58630

# 1- or 2-Channel 1 GHz A/D, 1- or 2-Channel 1 GHz D/A with Virtex-6 FPGA - 6U OpenVPX

Model 58630

#### Features

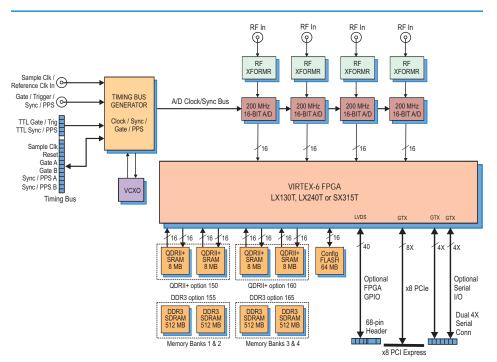

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- One or two 1 GHz 12-bit A/D

- One or two 1 GHz 16-bit D/A

- Up to 2 or 4 GB of DDR3 SDRAM; or: 16 MB or 32 MB of QDRII+ SRAM

- PCI Express (Gen. 1 & 2) interface up to x8

- Sample clock synchronization to an external system reference

- Dual-µSync clock/sync bus for multiboard synchronization

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

- Ruggedized and conductioncooled versions available

#### **General Information**

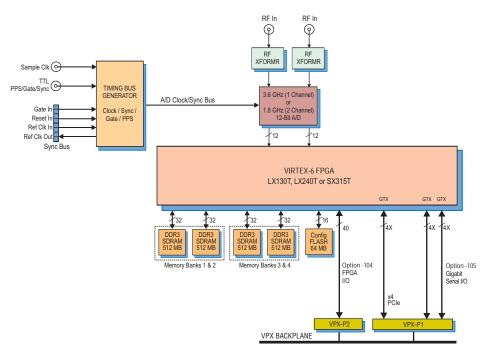

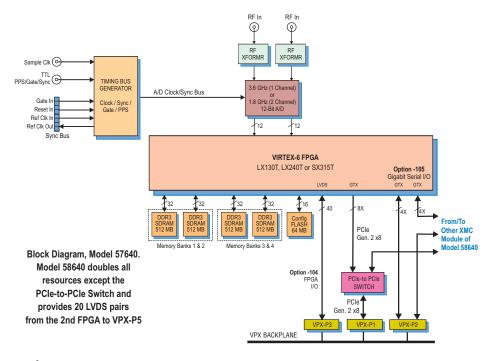

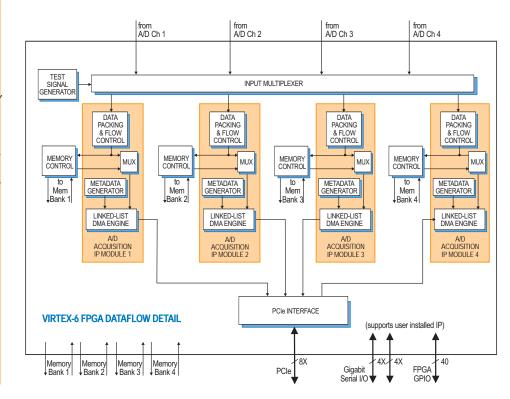

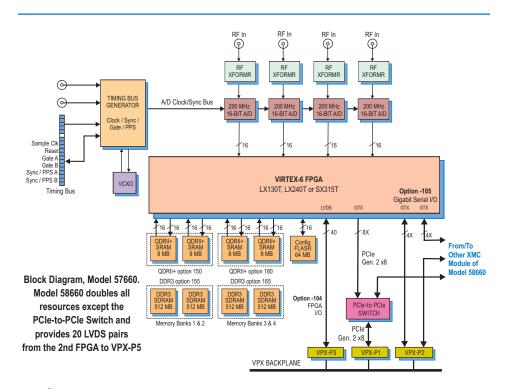

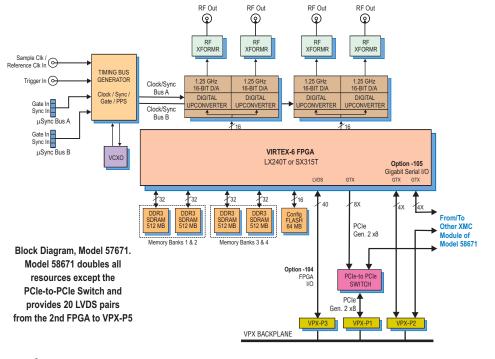

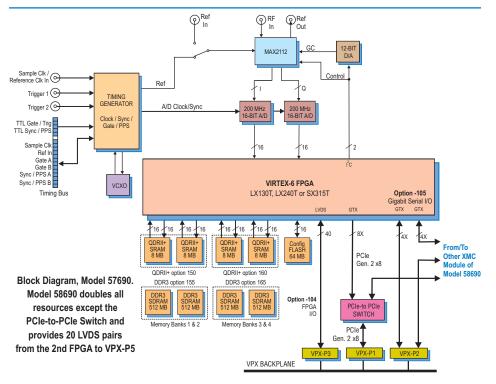

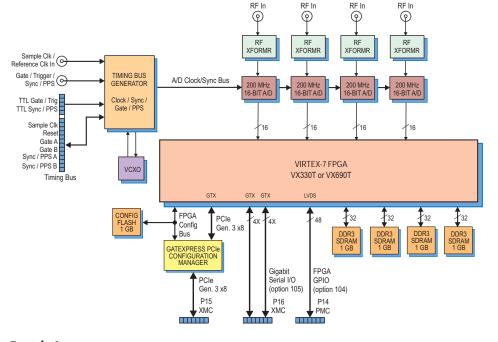

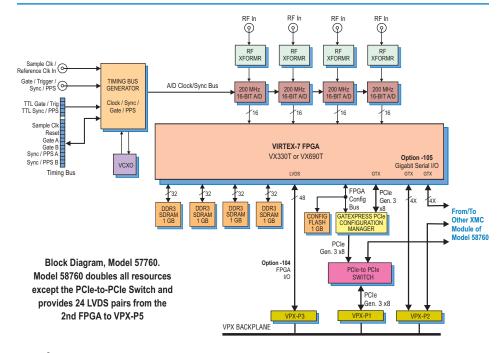

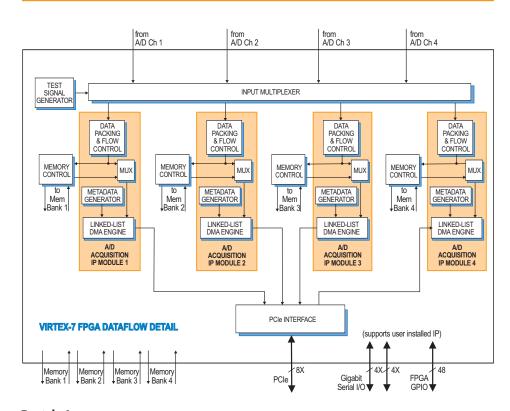

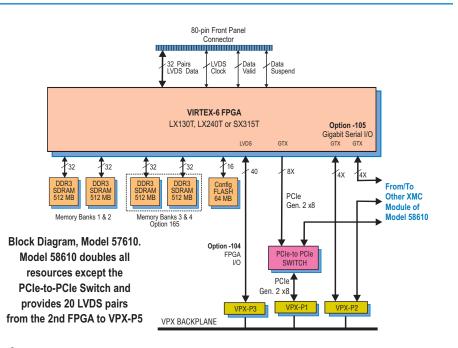

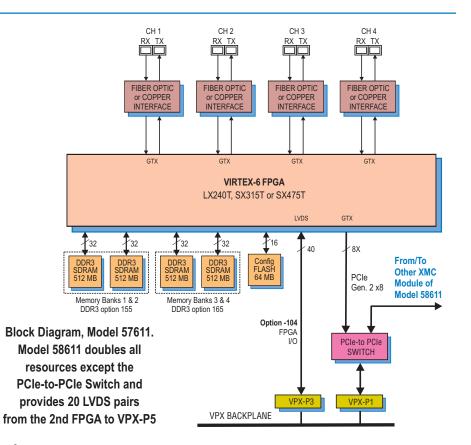

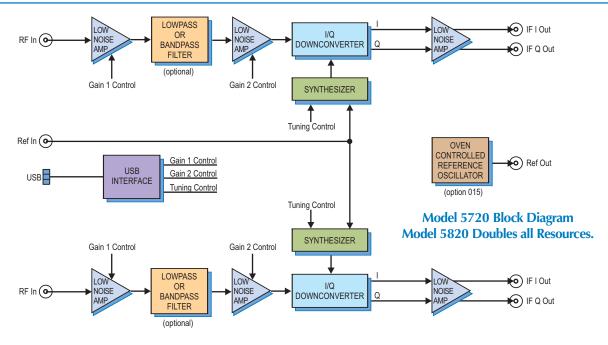

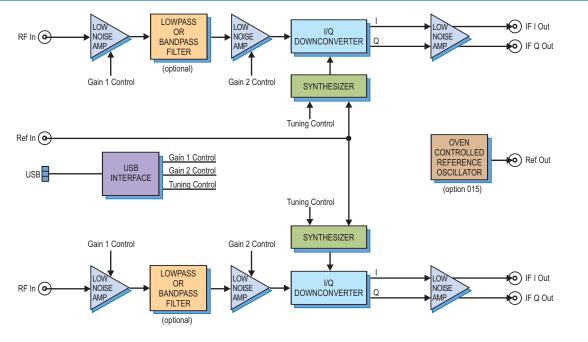

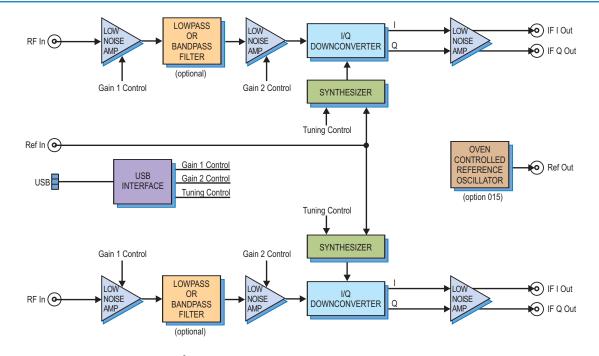

Models 57630 and 58630 are members of the Cobalt<sup>®</sup> family of high-performance 6U OpenVPX boards based on the Xilinx Virtex-6 FPGA. They consist of one or two Model 71630 XMC modules mounted on a VPX carrier board.

Model 57630 is a 6U board with one Model 71630 module while the Model 58630 is a 6U board with two XMC modules rather than one.

These models include one or two 1 GHz A/D and D/A converters and four or eight banks of memory

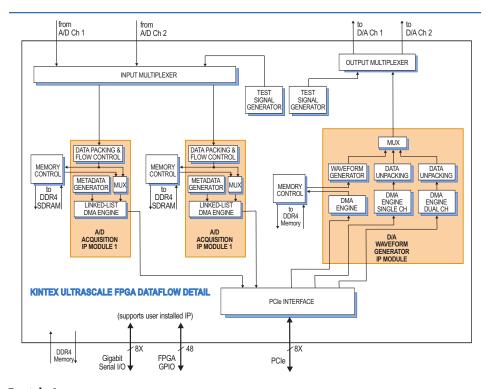

#### The Cobalt Architecture

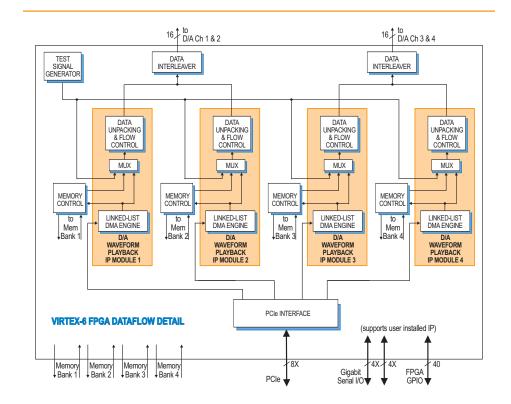

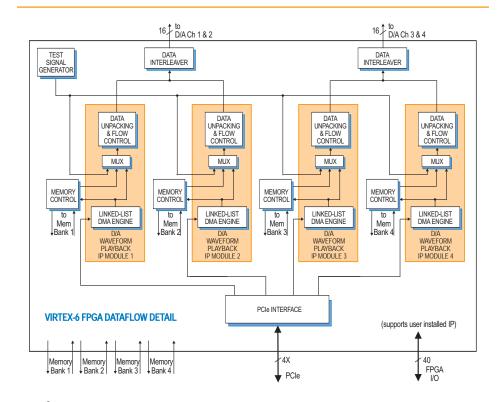

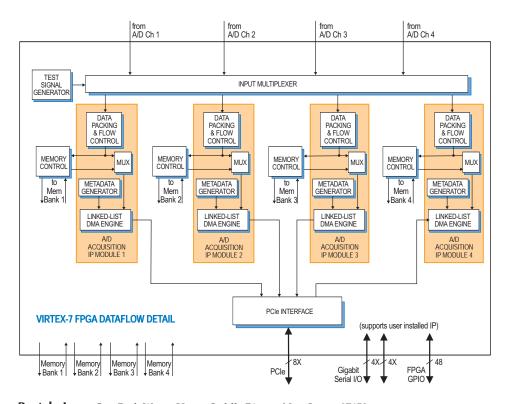

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The factory-installed functions of these models include one or two A/D acquisition and one or two D/A waveform playback IP modules. IP modules for either DDR3 or QDRII+ memories, controllers for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable these models to operate as complete turnkey solutions, without the need to develop any FPGA IP.

#### **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

#### **Xilinx Virtex-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

Option -104 provides 20 LVDS pairs between the FPGA and the VPX P3 connector, Model 57630; P3 and P5, Model 58630.

Option -105 supports serial protocalls by providing a 4X gigabit link between the FPGA and VPX P2, Model 57630; or one 4X link from each FPGA to P2 and an additional 4X link between the FPGAs, Model 58630. >

Pentek, Inc. One Park Way

Upper Saddle River

New Jersey 07458

Tel: 201·818·5900

Fax: 201·818·5904

Email: info@pentek.com

#### Models 57630 & 58630

## 1- or 2-Channel 1 GHz A/D, 1- or 2-Channel 1 GHz D/A with Virtex-6 FPGA - 6U OpenVPX

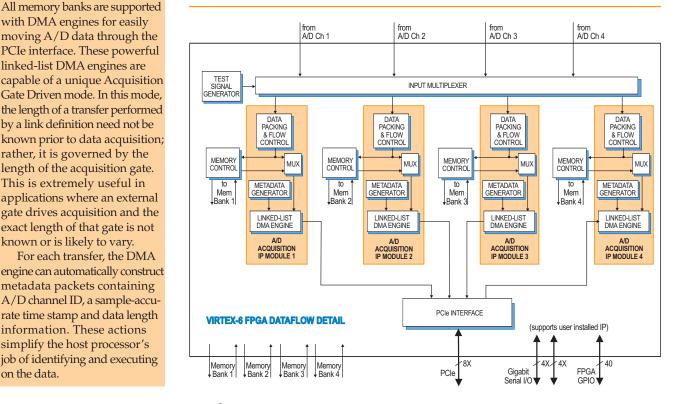

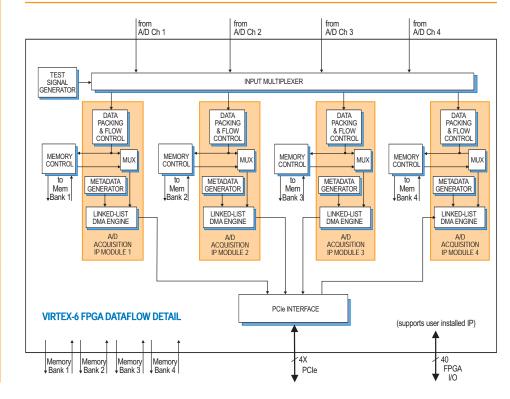

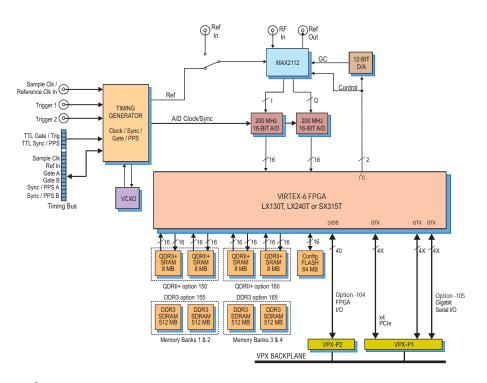

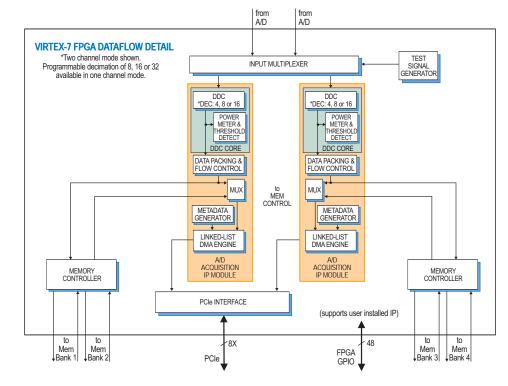

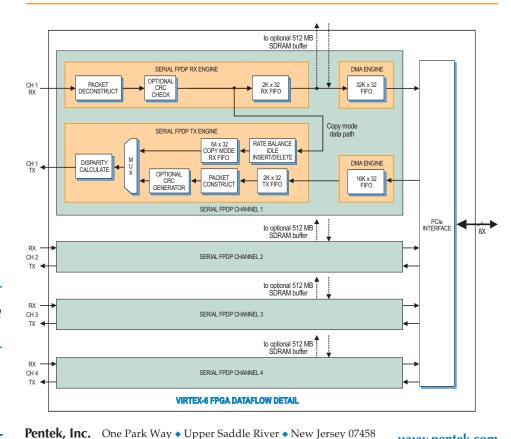

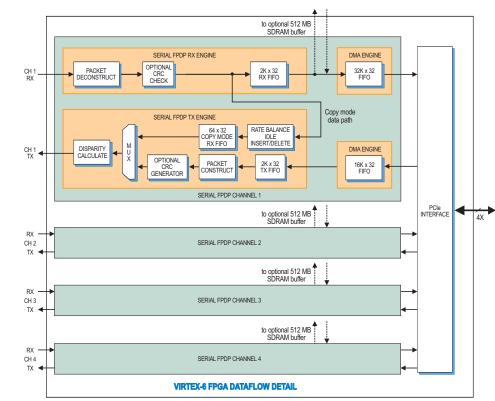

#### A/D Acquisition IP Module

These models feature one or two A/D Acquisition IP Modules for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

#### D/A Waveform Playback IP Modules

The factory-installed functions include one or two sophisticated D/A Waveform Playback IP modules. A linked-list controller allows users to easily play back waveforms stored in either on-board memory or offboard host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 or 128 individual link entries can be chained together to create complex waveforms with a minimum of programming.

#### ► A/D Converter Stage

The front end accepts one or two analog HF or IF inputs on front panel SSMC connectors with transformer coupling into one or two Texas Instruments ADS5400 1 GHz, 12-bit A/D converters.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

#### D/A Converter Stage

The 71630 features one or two TI DAC5681Z 1 GHz, 16-bit D/As. The converters have an input sample rate of 1 GSPS, allowing them to acept full rate data from the FPGA. Additionally, the D/As include a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4 rate input data. Analog output is through front panel SSMC connectors.

#### **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives a sample clock either from the front panel SSMC connector or from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this latter mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the VCXO. Either clock source (front panel or VCXO) can be used directly or can be divided independently by 2, 4, 8, or 16 to provide different lower frequency A/D and D/A clocks.

A pair of front panel  $\mu$ Sync connectors allows multiple boards to be synchronized. They accept CML inputs that drive the board's sync and gate/trigger signals.

The Pentek Model 9192 Cobalt Synchronizer can drive multiple µSync connectors enabling large, multichannel synchronous configurations. Also, an LVTTL external gate/trigger input is accepted on a front panel SSMC connector.

#### **Memory Resources**

The Cobalt architecture supports up to four or eight independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory. Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the module's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes. >

Pentek, Inc. One Park Way Upper Saddle River New Jersey 07458 Tel: 201818:5900 Fax: 201818:5904 Email: info@pentek.com

#### **Model 8264**

The Model 8264 is a fullyintegrated development system for Pentek Cobalt and Onyx 6U VPX boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

#### **Ordering Information**

| Model                            | Description                                                                                                                        |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 57630                            | 1 GHz A/D and D/A with<br>Virtex-6 FPGA - 6U VPX                                                                                   |  |

| 58630                            | Two 1 GHz A/D and D/A,<br>with two Virtex-6 FPGAs -<br>6U VPX                                                                      |  |

| <b>Options:</b>                  |                                                                                                                                    |  |

| -002*                            | -2 FPGA speed grade                                                                                                                |  |

| -062                             | XC6VLX240T FPGA                                                                                                                    |  |

| -064                             | XC6VSX315T FPGA                                                                                                                    |  |

| -104                             | LVDS I/O between the<br>FPGA and P3 connector,<br>Model 57630; P3 and P5<br>connectors, Model 58630                                |  |

| -105                             | Gigabit link between the<br>FPGA and P2 connector,<br>Model 57630; gigabit links<br>from each FPGA to P2<br>connector, Model 78630 |  |

| -160                             | Two 8 MB QDRII+<br>SRAM Memory Banks<br>(Banks 3 and 4)                                                                            |  |

| -155                             | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2)                                                                           |  |

| -165                             | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4)                                                                           |  |

| * This option is always required |                                                                                                                                    |  |

Contact Pentek for availability of rugged and conduction-cooled versions

#### Model Description

8264 VPX Development System. See 8264 Datasheet for Options

## 1- or 2-Channel 1 GHz A/D, 1- or 2-Channel 1 GHz D/A with Virtex-6 FPGA - 6U OpenVPX

#### ► PCI Express Interface

These models include an industrystandard interface fully compliant with PCI Express Gen. 1 and 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the board.

#### **Specifications**

Model 57630: 1 A/D, 1 D/A Model 58630: 2 A/Ds, 2 D/As Front Panel Analog Signal Inputs (1 or 2) Input Type: Transformer-coupled, front panel female SSMC connectors A/D Converters (1 or 2) Type: Texas Instruments ADS5400 Sampling Rate: 100 MHz to 1 GHz Resolution: 12 bits D/A Converters (1 or 2) Type: Texas Instruments DAC5681Z Input Data Rate: 1 GHz max. Interpolation Filter: bypass, 2x or 4x Output Sampling Rate: 1 GHz max. Resolution: 16 bits

Front Panel Analog Signal Outputs (1 or 2) Output Type: Transformer-coupled, front panel female SSMC connectors

Sample Clock Sources (1 or 2) On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

Clock Synthesizers (1 or 2) Clock Source: Selectable from on-board programmable VCXO or front panel external clock

**VCXO Frequency Ranges**: 10 to 945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phaselocked to an external 4 to 200 MHz system reference, typically 10 MHz **Clock Dividers:** External clock or VCXO

can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

#### External Clocks (1 or 2)

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

Timing Bus (1 or 2): 19-pin µSync bus connector includes sync and gate/trigger inputs, CML

External Trigger Input (1 or 2) Type: Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

Field Programmable Gate Arrays (1 or 2) Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2 or XC6VSX315T-2

Custom I/O

**Option -104:** Provides 20 LVDS pairs between the FPGA and the VPX P3 connector, Model 57630; P3 and P5, Model 58630

**Option -105:** Supports serial protocols by providing a 4X gigabit link between the FPGA and VPX P2, Model 57630; or one 4X link from each FPGA to P2 and an additional 4X link between the FPGAs, Model 58630

Memory Banks (1 or 2) Option 150: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR Option 155 or 165: Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

PCI-Express Interface

PCI Express Bus: Gen. 1 or 2: x4 or x8 Environmental: Level L1 & L2 air-cooled; Level L3 ruggedized, conduction-cooled Size: 3.937 in. x6.717 in. (100 mm x 170.6 mm)

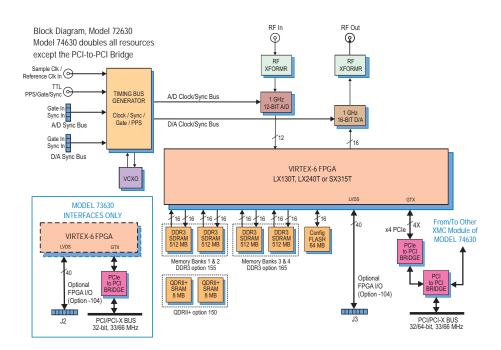

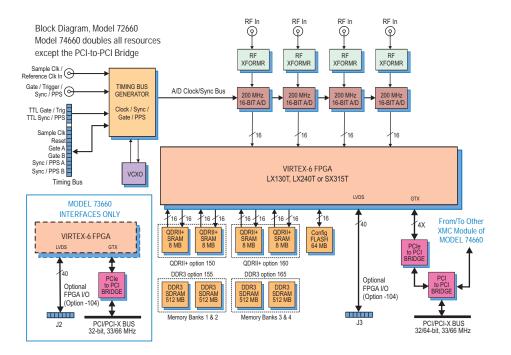

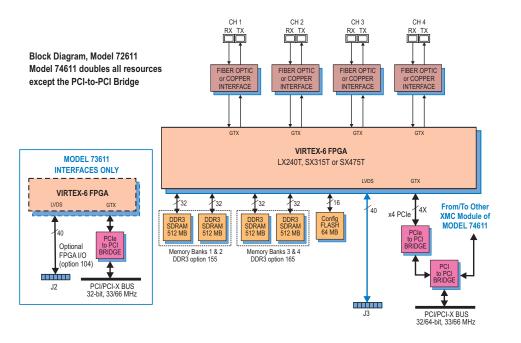

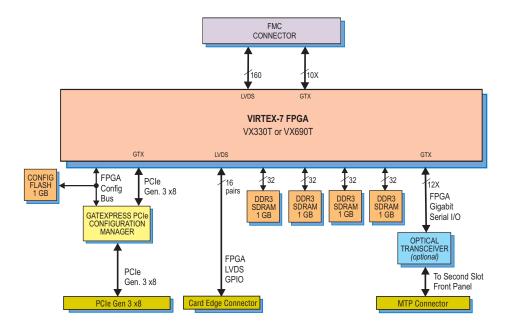

Model 74630 Model 73630

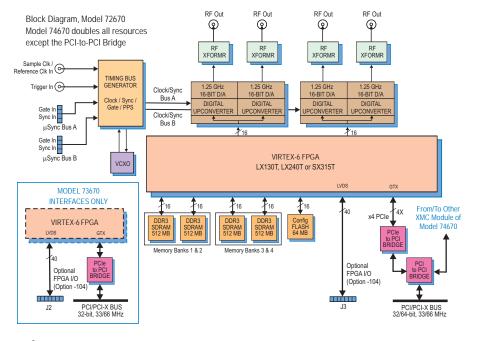

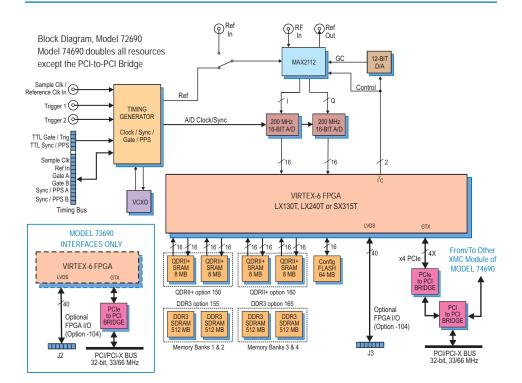

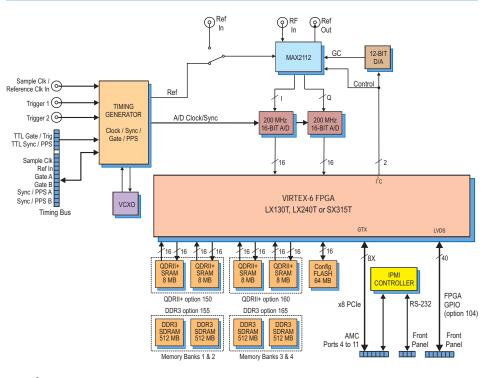

#### **General Information**

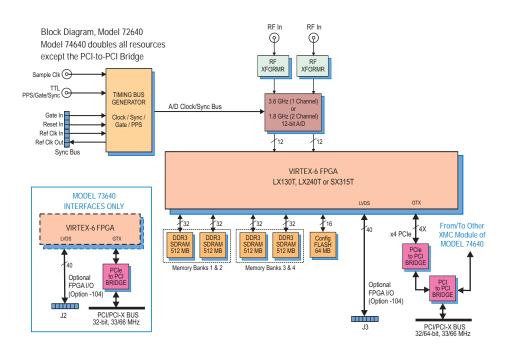

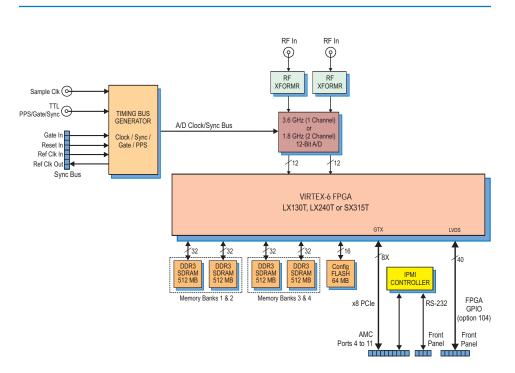

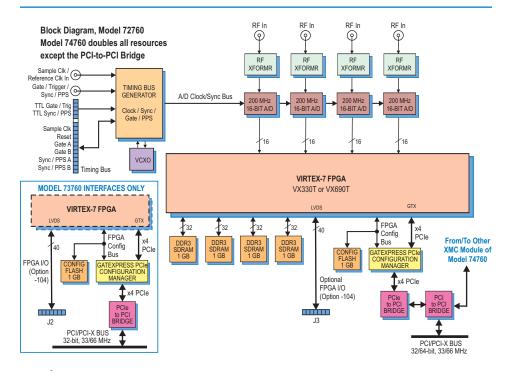

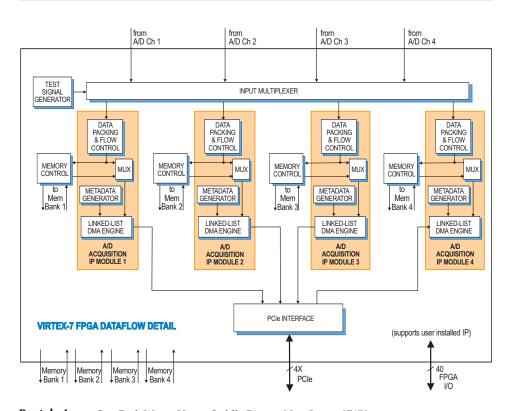

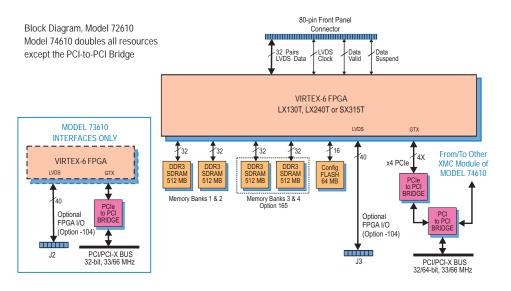

Models 72630, 73630 and 74630 are members of the Cobalt® family of high performance CompactPCI boards based on the Xilinx Virtex-6 FPGA. They consist of one or two Model 71630 XMC modules mounted on a cPCI carrier board.

Model 72630 is a 6U cPCI board while the Model 73630 is a 3U cPCI board; both are equipped with one Model 71630 XMC. Model 74630 is a 6U cPCI board with two XMC modules rather than one.

These models include one or two 1 GHz A/D and D/A converters and four or eight banks of memory

#### The Cobalt Architecture